新着情報

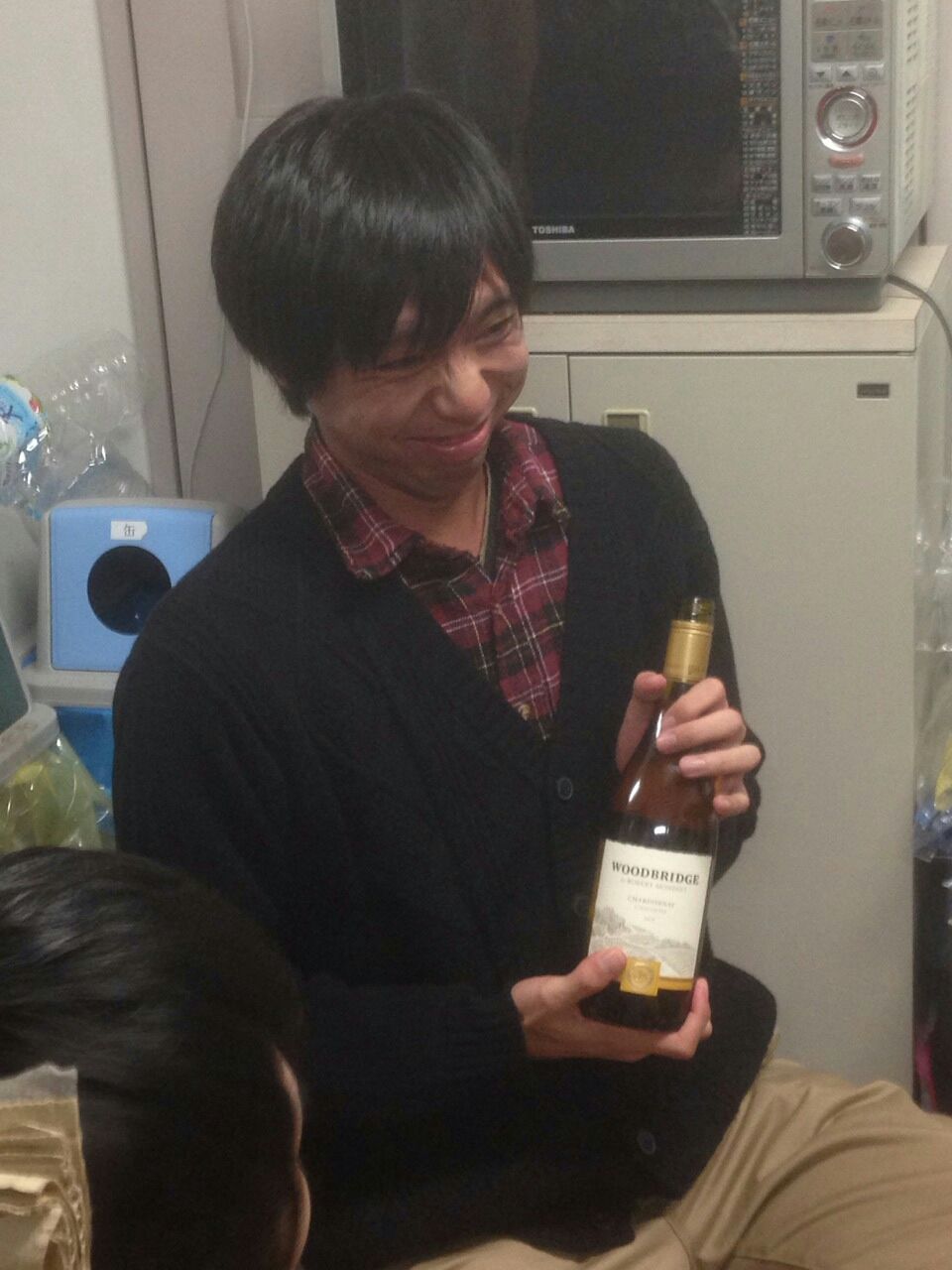

ワインを開けた犯人

image

published on

Self-introduction (old boy になりました --!!)

Hello, チャン ハオチェン(Zhang haosheng) 申します! I was assigned to do the self-introduction even though I’m already M2 student! Anyway I will finish this assignment because I’m always the “good boy” in my classmates and teachers !!! So who am I? This is a question… h_large_u3Kt_4f54000004911375 This is me, I like travelling, ride a horse and go around the wrold ! h_large_8X0q_5d5e00000161111a This is also me, I have a big house ….But it’s only a dream… Finally, this is the normal me….I’m a signle boy…残念だ。。 First thing I want to say is that I’m a boy and I like girls! This is very important because I’m too handsome and maybe quite dangerous in such men-love-men world. Ok back to normal. I was born in Zhejiang province, China. This area is so called 鱼米之乡 (means rich and comfortable place) since ancient time. And the west lake is the symbol of this area. It’s a very beautiful place, see the picture below. ky4lvC After high school, I left my hometown and went to Shanghai, the economy center of China. Actually it’s not so far from my hometown, maybe only one and a half hour by high speed train. And I study in Fudan university(复旦大学). It is one of the top 3 universities in China and has four beautuful campuses. I alwasy think it was very lucky for me to study in this universities for the past 4 years. Picture1 Me and my classmates @复旦大学 After graduation, I came to Japan in 2014. Japan is a very nice country, like food, scenary, and girls( most important). And I can always find something to do in this lab. It’s a nice choice to be here. And my future plan will be … let me think think ! Enjoy and enjoy ~~~~ to be continue….!

published on

中田さんお祝い飲み(早速)

image

published on

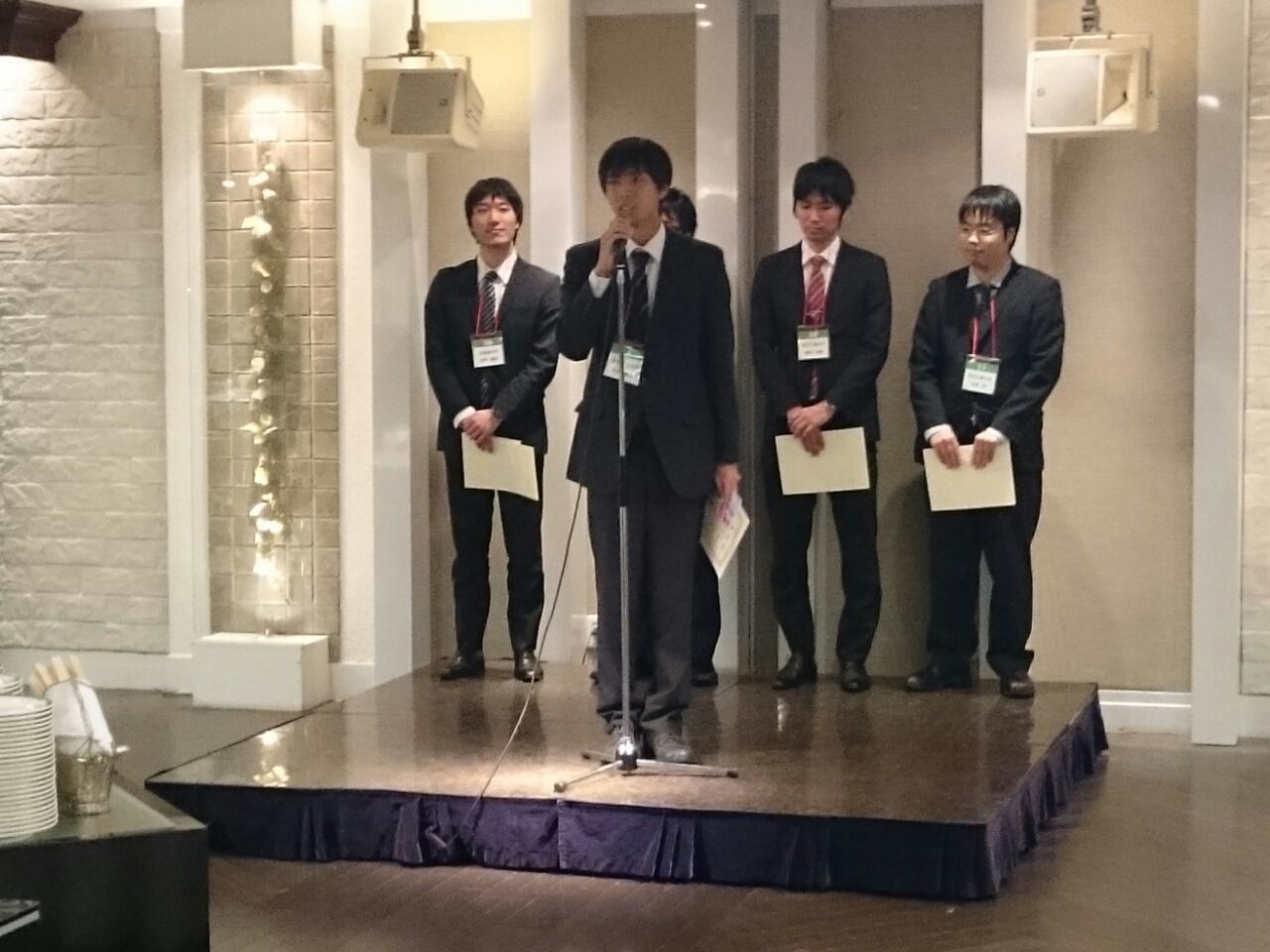

STARC Forum 中田さん最優秀賞受賞!

M2の中田さんが、STARC Forumで最優秀賞を受賞しました! image

published on

STARCフォーラム

これから、中田さん、永島さん、Liuさん、Aravindさん、Korkutさんが発表します! image

published on

ISSCC 2016

ISSCC 2016 (International Solid-State Circuits Conference)のプログラムが公開されました。ISSCCは半導体回路のオリンピックといわれる本分野最大の国際会議です。昨年に引き続き東工大からミリ波無線機について発表を行います。 今年は、同じセッション(2/2 Session 13 Wireless Systems)での発表です。13.3A 56Gb/s W-Band CMOS Wireless TransceiverK. K. Tokgoz, S. Maki, S. Kawai, N. Nagashima, J. Emmei, M. Dome, H. Kato, J. Pang, Y. Kawano, T. Suzuki, T. Iwai, Y. Seo, K. Lim, S. Sato, L. Ning, K. Nakata, K. Okada, A. MatsuzawaW-band(75-110GHz帯)を用い、無線回路として世界最速となる56Gb/sを実現しました。 13.6A 42Gb/s 60GHz CMOS Transceiver for IEEE 802.11ayR. Wu, S. Kawai, Y. Seo, N. Fajri, K. Kimura, S. Sato, S. Kondo, T. Ueno, T. Siriburanon, S. Maki, B. Liu, Y. Wang, N. Nagashima, M. Miyahara, K. Okada, A. Matsuzawa次世代WiFi規格であるIEEE802.11ayで必要となる64QAMによる42Gb/sの速度に、世界で初めて対応する無線集積回路に関する発表です。 通信速度としても、上記を除けば一番高速な無線通信を実現するものでしたが、発表者のWuさんは残念ながら世界最速の栄冠は逃してしまいました。。

published on

ミリ波で56Gビット/秒のデータレートを実現したトランシーバーIC(東京工業大学)@ISSCC2016

ISSCC2016での発表が日経テクノロジーで紹介されました!ミリ波で56Gビット/秒のデータレートを実現したトランシーバーIC http://techon.nikkeibp.co.jp/atcl/news/15/111801229/

published on

避難訓練

image 7階の逃げ遅れた人を救出中(訓練) image

published on

ASICON

Abdelさんが、IEEE ASICONで、Excellent Student Paper Certificate of Honorを受賞しましたー! DSC00893

published on

UESTC

電子科技大学(UESTC)のProf. Kai Kang先生を訪問しました。 DSC00757 そして同じ日の午後に別キャンパスのProf. Kaixue Ma先生を訪問しました。写真はMou先生。 DSC00766 次の日にASICONで講演。同じような話を3回したのでさすがに飽きました。。

published on

エレクトロニクス実装学会 講演大会@東工大 3/22-24

エレクトロニクス実装学会の講演大会@東工大の締め切りは 11/25 です。是非とも投稿ください! ==============================================================第30回エレクトロニクス実装学会春季講演大会 発表申込み募集のお知らせ 2016年3月22日-24日 東京工業大学 大岡山キャンパス 詳しくは以下のリンクを参照ください。 http://e-jisso.jp/event/taikai/030.html============================================================== 1.開催概要> 1)日時: > > 2016年3月22日(火)から24日(木) > > > > > 2)場所: > > 東京工業大学 大岡山キャンパス:西9号館(講演セッション、ポスターセッション、ものづくりセッション) > > 東工大蔵前会館くらまえホール(予定)(表彰式、特別講演、交流会) > > 地図 http://www.titech.ac.jp/maps/index.html 2.講演セッション> 「講演セッション」は、最新の実装技術分野の研究成果を発表し、議論するセッションです。 > > > > > 2)予稿: > > 論文形式でA4サイズ1~4頁 > > > > > 3)講演: > > 15分(発表時間12分、討論時間3分) > > > > > 4)講演内容: > > 最近行った研究および調査の報告、または成果をあげた試験結果や技術開発の報告等で、学術的・工業的に価値の

published on

バレンタイン17年

image

published on

肉

いまから、肉食います! image

published on

welcome party

image

published on

Apple

ISSCCのTPC meetingの後、CupertinoのApple本社を訪問し、本研究室OBのDr. Wei Deng氏と会談を行いました(岡田)。研究生活をEnjoyしているそうです! DSC00698

published on

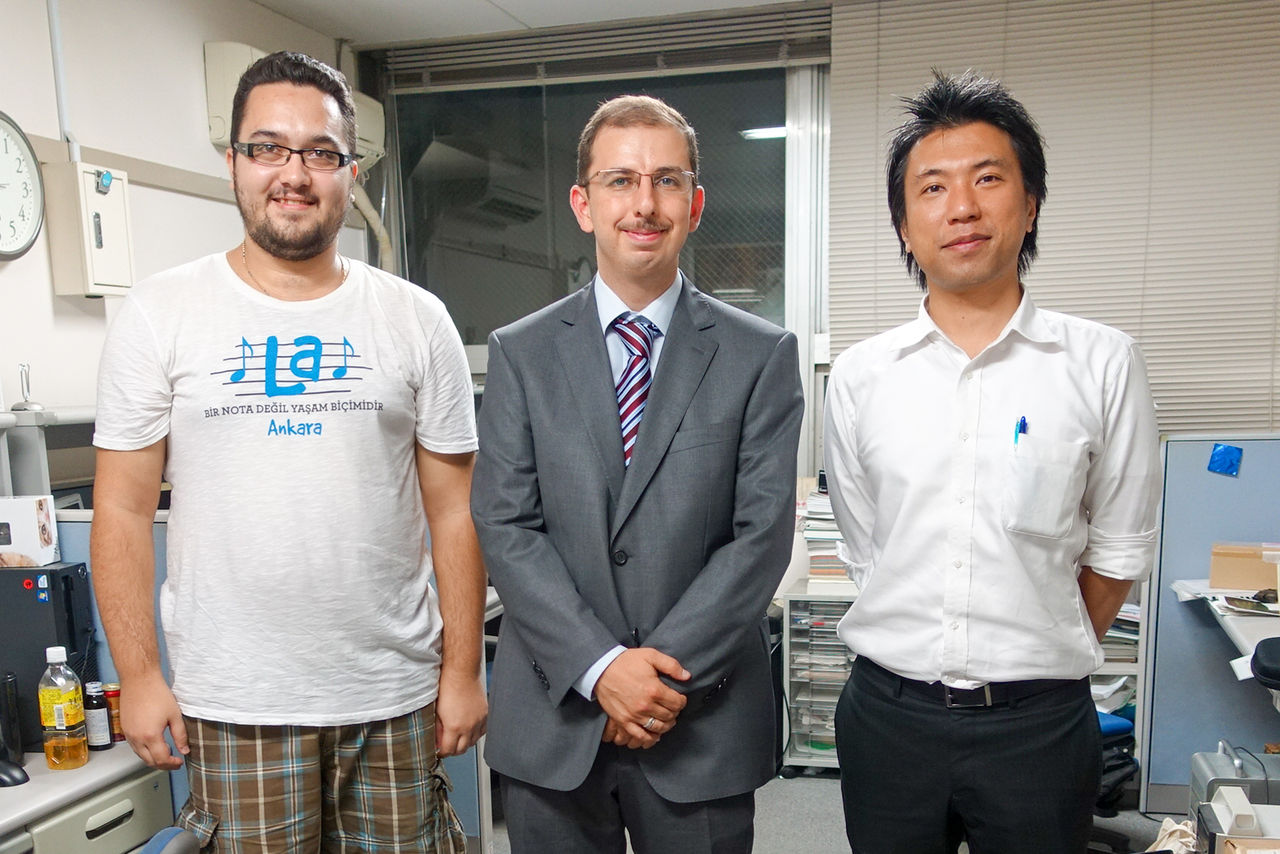

Prof. Mehmet Unlu

Prof. Mehmet Unlu visited our laboratory.

DSC00190

published on

M2就活お疲れ飲み

2次会なう image

published on

投稿お疲れ様でした!

IMG_2352

published on

電子情報通信学会 ソサイエティ大会 @東北大

通信学会@東北大に参加してきました! DSC00074 仙台といえば牛タン!ということで食文化を研究したり DSC00057 DSC00056 松島で自然を観察したり DSC00157 DSC00141 DSC00164 キリンの工場でビールの作り方を勉強したりしました。 DSC00026 07-2 DSC00046 発表日は豪雨で電車・バスが止まっており、駅から40分ほど歩く羽目に…。 DSC00064 DSC00067 DSC00068 DSC00069 DSC00070 DSC00071 DSC00072 DSC00097 DSC00101 学会終了後に伊達政宗と記念撮影。 DSC00087 以上です!

published on

For Foreign Students

International Graduate Program http://www.titech.ac.jp/english/globalization/stories/international_graduate_program.html

See also this.

published on