新着情報

研究室で花見を行いました。

雨もやみ、少し寒い中でしたが、楽しい時間を過ごしました。

学位記授与式が執り行われ、当研究室の二人が代表に選ばれました。

東京科学大学学位記授与式が執り行われ、当研究室から山崎雄大さんが電気電子コースの博士課程修了生代表に、伊藤浩太郎さんが電気電子系からの学士課程卒業生代表を務めました。

卒業・修了おめでとうございます!

~新歓お花見会のお知らせ~

4月2日(木)の夕方にお花見をします!🌸

当日、岡田研に配属が決まった方はぜひご参加ください!

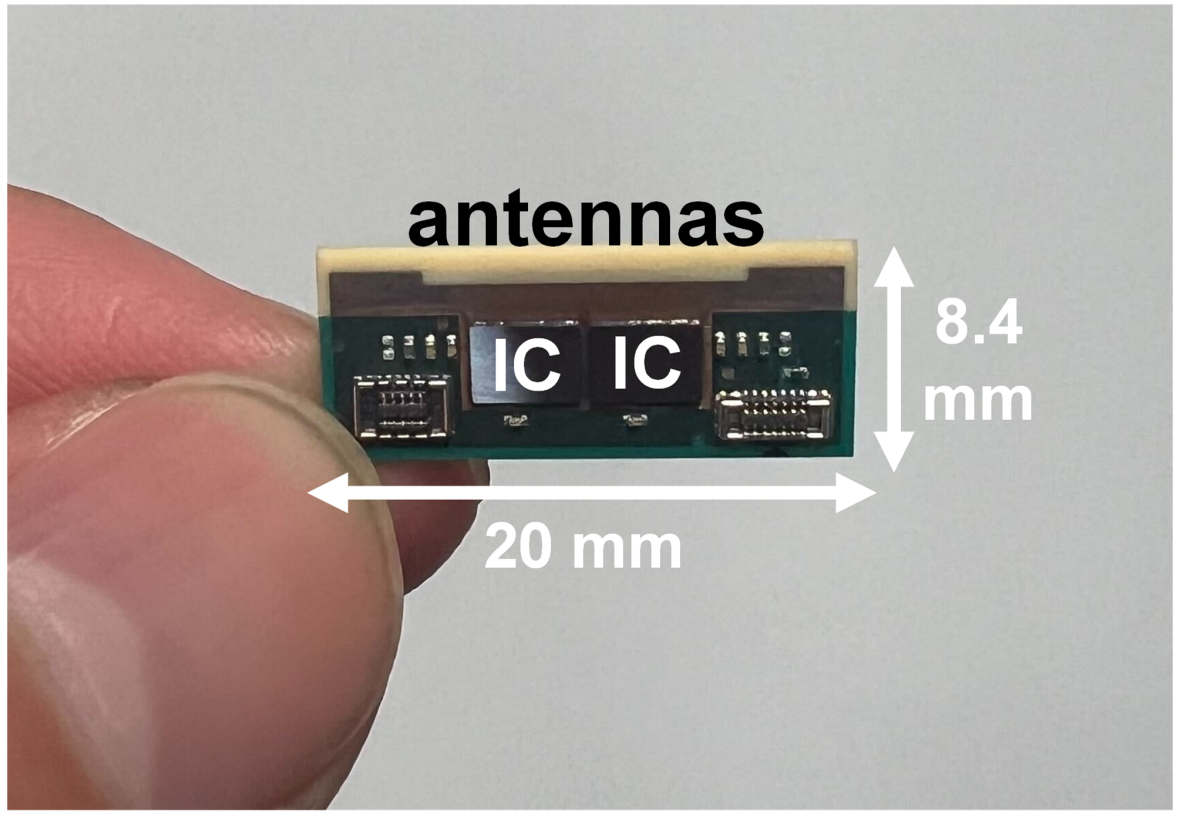

山崎雄大さんの6G端末向け150 GHz帯アンテナ一体無線機モジュールに関するJSSC論文が発表されました。

山崎雄大さんの、6G端末向けの150 GHz帯アンテナ一体無線機モジュールに関するJSSC論文が発表されました。

本論文は、2025年6月13日発表の「150 GHz帯超小型・低消費電力アンテナ一体無線機モジュールを開発」に関連する成果です。

参考URL:

山崎雄大さんが、2026年2月にサンフランシスコで開催されたISSCC 2026においてStudent Research Preview Poster Awardを受賞しました。

ISSCC 2026にて、山崎雄大さんのStudent Research Preview(SRP)でのポスター発表が高く評価され、Poster Awardを受賞しました。おめでとうございます!

ポスタータイトル:A High-Power-Density D-Band Phased-Array Transceiver in 65nm CMOS for 6G UE Module

開催案内:2026年 工学院 電気電子系 大学院説明会(大岡山・すずかけ台)

工学院 電気電子系では、電気電子系への入学・進学を検討している方を対象に、大学院説明会を開催します。

主に修士課程に関する説明と研究室紹介を行います。

いずれの回も、現地会場とZoomを併用したハイブリッド形式で実施します。

大学院入学を検討されている方は、ぜひご参加ください。

入試制度や募集要項などの詳細については、大学の入学案内ページもあわせてご覧ください。

■開催日時

第一回 大岡山 2026年3月27日(金) 13:00〜17:00

第二回 すずかけ台 2026年5月15日(金) 13:00〜17:00

■プログラム

電気電子系への入学・進学を検討している方を対象に大学院説明会を行います。主に修士課程に関する説明と研究室紹介になります。

13:00〜14:00 電気電子系大学院入試説明会

14:00〜17:00 研究室見学会

■開催場所

第一回 3月27日(金) 大岡山キャンパス 南2号館 S2-204(S221)講義室/ハイブリッド(Zoom)

第二回 5月15日(金) すずかけ台キャンパス J2棟 J2-203講義室(予定)/ハイブリッド(Zoom)

■対象者

大学院入学を希望する学部生および大学院生

工学院/電気電子系の入学を検討している方

2027年4月/2026年9月より入学を希望する方

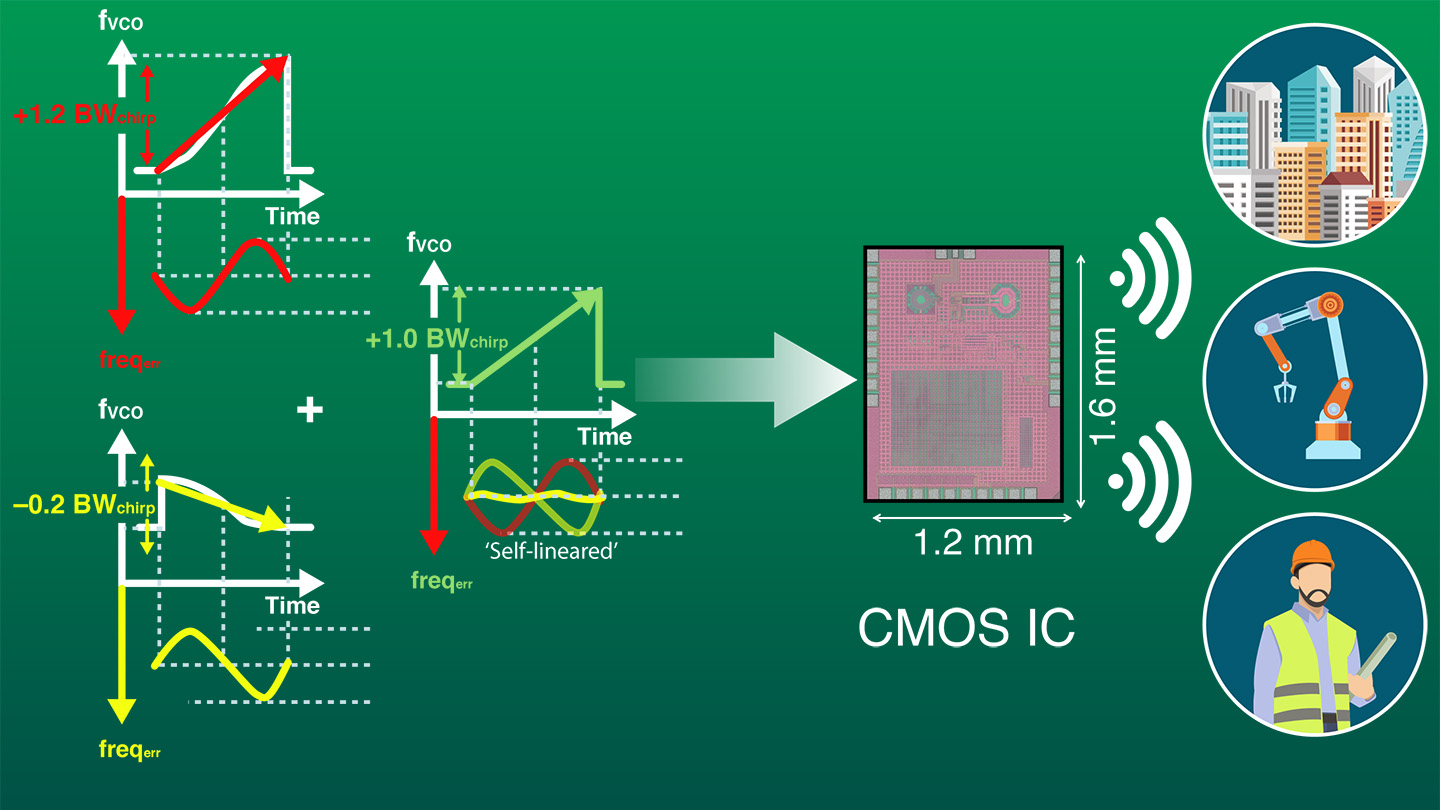

高性能FMCWレーダー用信号発生器CMOS ICを開発

Prof. Hua Wang

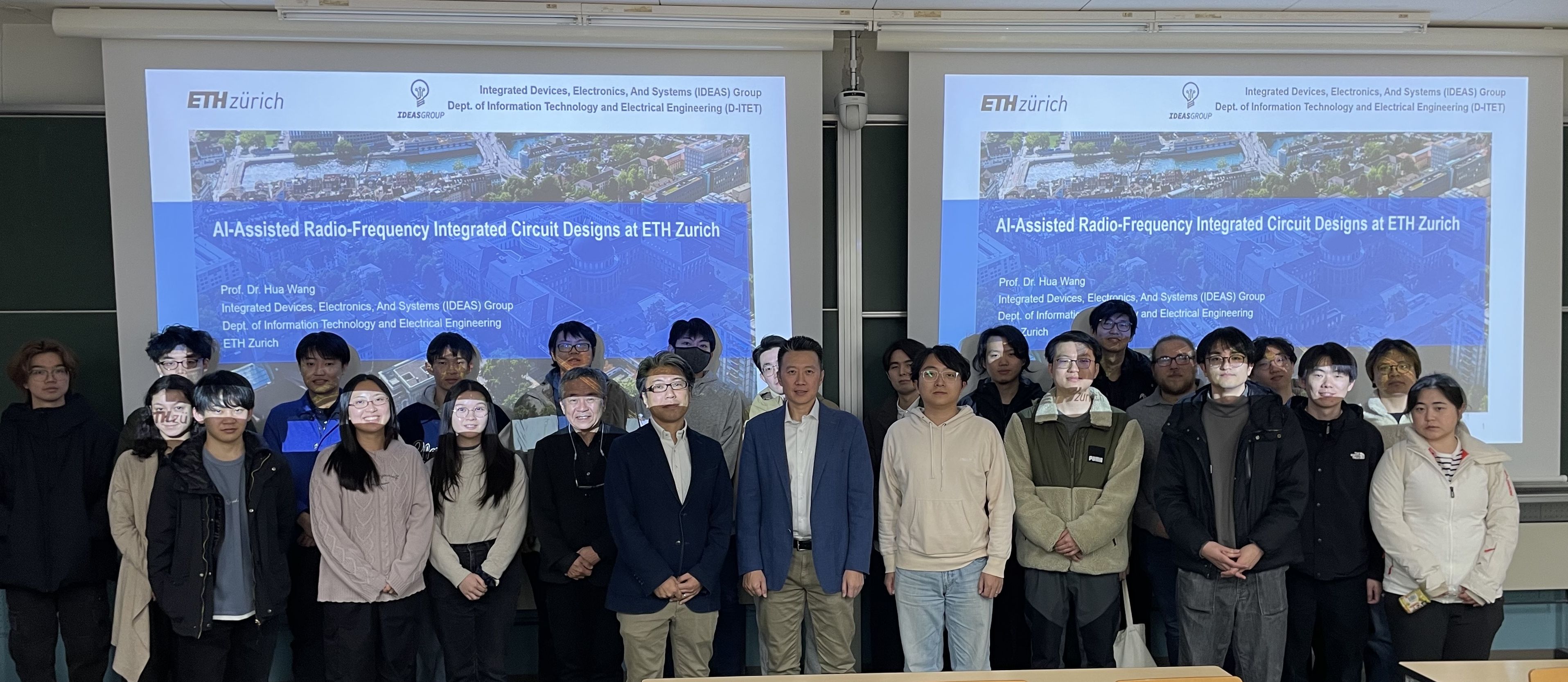

ETH Zurich(スイス連邦工科大学チューリッヒ校)の Hua Wang教授にご講演頂きました。

Speaker: Prof. Hua Wang (ETH, Zurich, Swiss)

Title: AI-Assisted for Radio-Frequency Integrated Circuits at ETH Zurich

Abstract: In recent years, as AI for Science is gaining increasing momentum, there are rapidly growing interest in applying AI tools to facilitate RFIC designs or explore new design spaces. In this seminar talk, I will present a few on-going AI4RF projects at my IDEAS group at ETH Zurich. We will start with our project of AI-assisted template-seeded pixelated design for multi-metal-layer EM structures, which explores a new approach for efficient exploration and exploitation of the design space. Next, we will introduce our transfer learning assisted fast design migration, which potentially enables efficient design migrations over technology nodes and operating frequencies. Finally, we will present out project on top-metal-only RFIC redesigns for fast specs-to-silicon iteration enabled by AI-assisted inverse design. Finally, we will discuss challenges and future directions.

Prof. Mehdi Saligane

Brown University(米ブラウン大学)の Mehdi Saligane先生にご講演頂きました。

Speaker: Prof. Mehdi Saligane (Brown University, USA)

Title: AI for Chips & Chips for AI

Abstract: The exploding scale of modern applications is stretching yesterday’s integrated-circuit (IC) design flows beyond their limits. This talk presents a unified, open, and highly-automated paradigm—AI for Chips & Chips for AI—that simultaneously (i) harnesses artificial intelligence in EDA to build better silicon and (ii) architects silicon that runs AI better.

AI for Chips - Traditional analog layout still relies on expert heuristics. We introduce Agentic-RL gLayout, a goal-conditioned reinforcement-learning agent that replaces hand-tuned placement and routing with policy-driven planning, action, and self-correction. The agent ingests high-level objectives, observes the evolving layout state, and chooses between primitive commands and high-level macros. Positive rewards track goal attainment; penalties capture DRC violations, area bloat, and parasitics, producing cleaner, compact, and rule-compliant layouts without manual intervention. Built atop open-source engines such as OpenROAD, Open Se Cura, and OpenFASoC, the framework pushes layout quality while democratizing access to sophisticated analog design automation. Chips for AI - Conversely, deploying large language model (LLM) workloads at the edge demands silicon tuned for extreme efficiency. We unveil a hardware–software co-design stack centered on ConSmax, a highly parallel, element-wise alternative to Softmax that slashes latency and energy. By co-optimizing network topology, arithmetic precision, and accelerator micro-architecture, the framework meets sub-millisecond deadlines, preserves privacy, and cuts cloud dependence.

Finally, this talk will walk through an open chip design infrastructure augmented with LLM-guided code, circuit, and layout generation that turns hardware creation into a rapid feedback loop, where AI sharpens the EDA tools, while tailored accelerators speed up AI. Closing the “AI-for-chips, chips-for-AI” cycle should make taping-out test chips possible in weeks instead of years, thus propelling the next wave of semiconductor innovation.

Bio: Mehdi Saligane received the B.S. and M.S. degrees in Electrical Engineering Systems and Industrial Computing from École Polytechnique de Grenoble in 2009, and the M.S. Degree in electrical engineering from the University of Grenoble in 2011, and the Ph.D. degree in Electrical Engineering and Computer Science from the University of Aix-Marseille (IM2NP), France, in 2016. From 2010 to 2015, he was part of the Central Research and Development Group at STMicroelectronics in Crolles, France, focusing on adaptive, ultra-low-power digital design. In 2015, he joined the Michigan Integrated Circuit Laboratory at the University of Michigan, Ann Arbor, MI, USA, as a visiting research investigator. In 2019, he served as a Visiting Researcher at the University of California, San Diego, San Diego, CA, USA. He is a founding member of both the OpenROAD and OpenFASOC Projects. Since 2020, he has been a Research Faculty member at the University of Michigan. In 2024, he joined Google Research as a Visiting Faculty Member, and in 2025, he joined Brown University as an Assistant Professor of Electrical and Computer Engineering. His research interests include secure low-power and energy-efficient IC design, Biosensors, analog/mixed-signal design automation and open-source EDA, and custom architectures for lightweight language model accelerators. Dr. Saligane is the recipient of the 2023 Google Cloud Research Innovators Award and the 2021 Google Research Faculty Award. He served in leadership roles at the CHIPS Alliance from 2020 to 2023, including as Chair of the Analog Working Group and as a member of the Technical Steering Committee. Since 2020, he has served on the IEEE Solid-State Circuits Society (SSCS) Open-Source Ecosystem (TC-OSE) Technical Committee and has been the Chair since 2025. In addition, he co-founded and organizes the SSCS Chipathon Design Contest and the SSCS Code-a-Chip Notebook Competition at ISSCC and VLSI Symposium, fostering student engagement with open-source chip design.

ISSCC 2026で4件発表

ISSCC 2026で発表します!

Forum Presentation

- Kenichi Okada, “Exploration of 6G FR3 for Coverage, Capacity, and Sensing in Edge AI Era”

Regular Session

- Daxu Zhang, et al., “A 9.7GHz Self-Linearized-VCO-Based FMCW Chirp Generator Achieving 1.56GHz/µs Slope and 0.57µs Duration with 0.094% rms Frequency Error”

Dongfan Xuさん、Minghao Fanさんが、Student Research Previewで発表します。

Prof. Jeffrey S. Walling

Virginia Tech(バージニア工科大学)の Jeffrey S. Walling教授にご講演頂きました。

Speaker: Prof. Jeffrey S. Walling (Virginia Tech, USA)

Title: Bits-to-Waves: Digital RF, mm-Wave and THz Systems to Enable the Next-G

Abstract: Mixer-based transmitters have been dominant for approximately 100 years. However, for more than a decade RF-DACs have demonstrated the ability to combine the functionality of the DAC, upconverter and amplification stages of a transmitter into a single block. The switched-capacitor power amplifier (SCPA) is a versatile RF-DAC that operates in a voltage mode and uses transistors only as switches. This talk provides a tutorial introduction of the SCPA and presents architectural examples that enable both frequency reconfigurability and operation up to mm-Wave, supporting up to 3Gb/s transmission rates. New uses of algorithmic designs for RF passives will also be introduced.

Speaker Bio: Jeff Walling received his BS from University of South Florida and his MS and PhD from University of Washington, all in Electrical Engineering. He has held industrial positions at Motorola, Intel, Qualcomm and Skyworks. His research has primarily focused on circuits for wireless communications and sensing. From 2012 to 2019, he was an assistant, then associate professor at University of Utah. Then he was head of RF transceivers at Tyndall National Institute in Cork, Ireland. Since 2021, he is an associate professor at Virginia Tech. He has served as an associate editor for TCAS-II, TCAS-I and JSSC, and on the technical program committees of the IEEE RFIC, ISSCC and NEWCAS conferences. He is a senior member of the IEEE and has more than 80 papers in peer reviewed conferences and journals.

A-SSCC 2025

韓国のDaejeonで開催されたIEEE Asian Solid-State Circuits Conference (A-SSCC)で発表しました.

Dongfan Xu, Minzhe Tang, Haiyun Gu, Ziyuan Ren, Yilun Chen, Minghao Fan, Yuxuan Liu, Daxu Zhang, Yi Zhang, Zheng Li, Yuncheng Zhang, and Kenichi Okada,

“A Ka-Band Time-Modulated Variable Gain Amplifier with 30-dB Gain Tuning and <2° Phase Variation via Duty Cycle Control”

Sunghwan Park, Yudai Yamazaki, Carrel de Gomez, Chenxin Liu, Jun Sakamaki, Hiroyuki Sakai, Kazuaki Kunihiro, and Kenichi Okada,

“A High-Efficient 154GHz 4TX/4RX FMCW Radar Chipset in 65nm CMOS”

Kenichi Okada“How to cultivate good chip designers” Panel discussion

“Millimeter-Wave Circuit Innovations for 6G and Beyond”

KAIST EE Global Symposium

IEEE/IEIE ICCE Asia“Millimeter-Wave Circuit Innovations for 6G and Beyond”

also presented at Seoul National Univerisity

研究室紹介

論文投稿完了!

論文投稿完了したところで記念撮影しました!

2025年度 OB/OG会を開催

2025年8月23日 OB/OG会を開催しました!

OB/OG MLが届いていない人は secretary@ssc.p.isct.ac.jp まで連絡ください!

山崎雄大さんが、MCRG研究会で最優秀ポスター発表を受賞しました!

2025年度第2回MCRG(Mobile Commuication Research Group)研究会にて、山崎雄大さんが最も優秀なポスター発表を行った研究者と認定されました。 おめでとうございます!

発表ポスタータイトル: 「次世代無線端末の実現に向けた 超小型サブテラヘルツ半導体無線機」

Prof. Chung-Tse Michael Wu

国立台湾大学のChung-Tse Michael Wu先生に訪問いただきました!

Prof. Yu-Hsiang Cheng

国立台湾大学のYu-Hsiang Cheng先生に訪問いただきました!

Prof. Mark Rodwell

UCSBのMark Rodwell教授にご講演頂きました!

Lecturer: Prof. Mark Rodwell(University of California, Santa Barbara)

Title: 100-300 GHz Wireless: transistors, ICs, systems

Date & Time: Tuesday, July 15, 2025, 15:45 – 17:30

Abstract: We describe the opportunities, and the research challenges, presented in the development of 100-300GHz wireless communications and imaging systems. In such links, short wavelengths permit massive spatial multiplexing both for network nodes and point-point links, permitting aggregate transmission capacities approaching 1Tb/s. 100-300GHz radar imaging systems can provide thousands of image pixels and sub-degree angular resolution from small apertures, supporting foul-weather driving and aviation. Challenges include the mm-wave IC designs, the physical design of the front-end modules, the complexity of the back-end digital beamformer required for spatial multiplexing, and, for imaging, the development of system architectures requiring far fewer RF channels than the number of image pixels. We will describe transistor development, IC design, and system design, and describe our efforts to develop 140GHz massive MIMO wireless hubs, and 210GHz and 280GHz MIMO backhaul links.

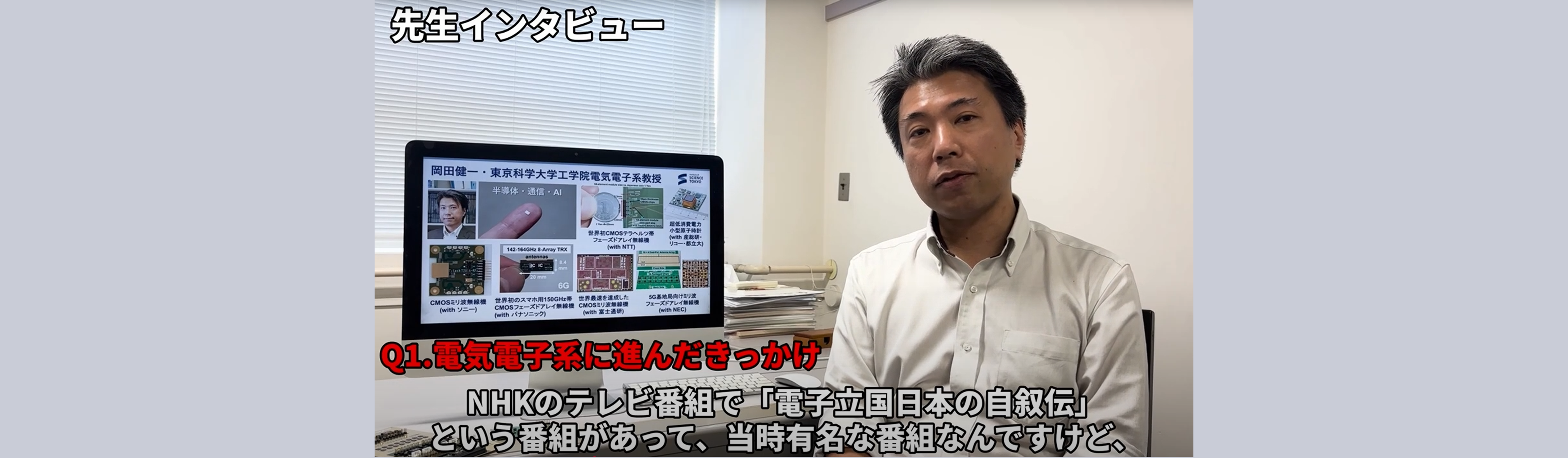

山崎雄大さん、第38回独創性を拓く先端技術大賞「文部科学大臣賞」を受賞

優れた研究成果を上げた理工系の学生や企業の若手研究者らを表彰する「第38回 独創性を拓く 先端技術大賞」(主催・産経新聞社、後援・文部科学省、経済産業省、ニッポン放送、特別協力・アカリク)の授賞式が7月14日、高円宮妃久子さまをお迎えして東京・元赤坂の明治記念館で開かれ、博士課程の山崎雄大さんが学生部門の最高賞である「文部科学大臣賞」を受賞しました。