新着情報

ISSCC 2025

Eveninig Panel: “Future of Analog Design: Still Magical or Mostly Digital?”

Forum: Wireless Communication Technology for Space Applications: From Satellite to Dish and Smartphones

Kenichi Okada, Institute of Science Tokyo, Tokyo, Japan

“Foldable Phased-Array Transceivers for Satellite Communications”

published on

Xu Dingxinさんが、IEEE SSCS Predoctoral Achievement Award受賞

Xu Dingxinさんが、IEEE SSCS Predoctoral Achievement Awardを受賞しました!

published on

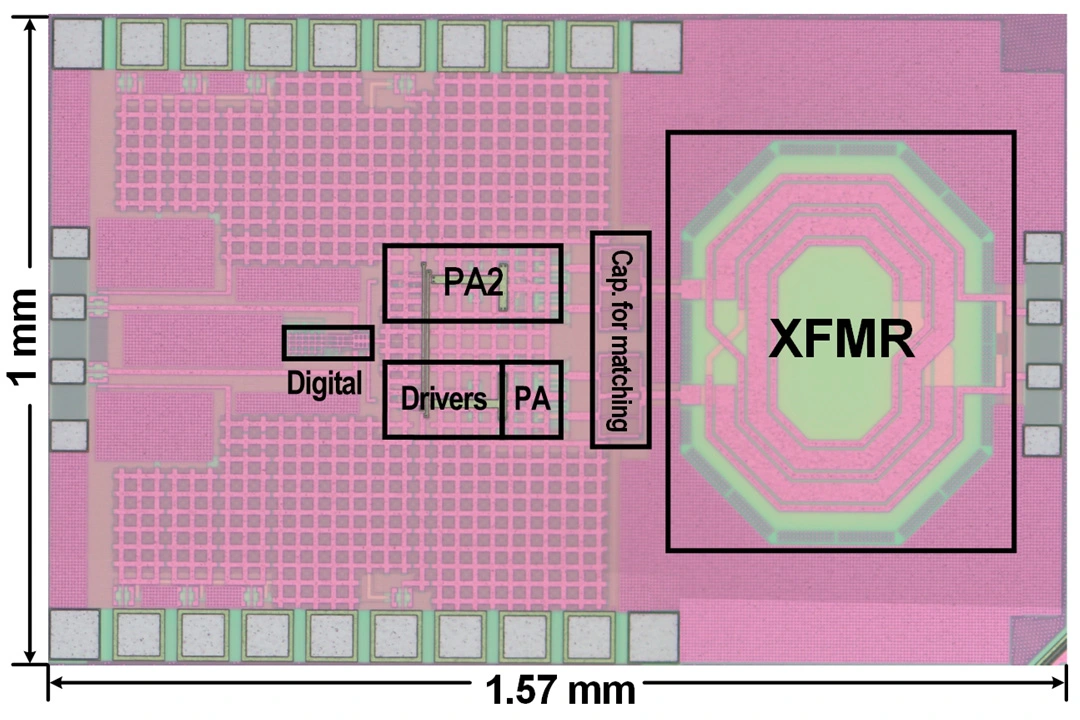

Beyond 5Gに向けた新型デジタル送信機CMOS ICを開発

高電力効率と線形性を両立する無線通信用送信機CMOS ICを開発 複雑なコーディックを使用しない新しいデジタル送信機のアーキテクチャを提案 小型・低消費電力でさまざまなIoT機器に搭載可能であり、IoTの普及に貢献

published on

ISSCC 2025で6件発表

ISSCC 2025で発表します! Forum Presentation Kenichi Okada, “Foldable Phased-Array Transceivers for Satellite Communications” Regular Session Yuncheng Zhang, et al.,“A Power-Efficient CORDIC-less Digital Polar Transmitter Using 1b DSM-Based PA Supporting 256-QAM” Sena Kato, et al.,“A 256-Element Ka-Band CMOS Phased-Array Receiver Using Switch-Type Quadrature-Hybrid-First Architecture for Small Satellite Constellations” (白根研) 山崎雄大さん、Minzhe Tangさん、Daxu Zhangさんが、Student Research Previewで発表します。

published on

益先生 最終講義 2025/3/8

益先生の最終講義、2025/3/8です! 是非、ご参加ください! ●益 一哉先生 最終講義とお祝いの会のご案内 https://x.gd/UnSnO (聴講も申し込みが必要です) 〇最終講義 「未来を先送りしない」 日時:2025年3月8日(土) 14時~16時 (受付開始:13時) 場所:東京科学大学 大岡山キャンパス 蔵前会館 方法:ハイブリッド開催(オンサイト+zoom配信) 登録:https://forms.gle/3nkAVDsJ8oCcrmCRA (2月3日まで) 〇懇親会 日時:2025年3月8日(土) 18時~20時 (17時30分 開場) 場所:新横浜プリンスホテル 5階 シンフォニア 申込 https://forms.gle/s4X1tTcJeWBWcpXX7 (2月3日まで) ●連絡先 masulecture@nasu.iir.titech.ac.jp 最終講義 「「未来を先送りしない」 益 一哉 私は、1982年から半導体集積回路の研究を大学で行い、2024年9月まで東工大学長を務め、現在産総研に勤務しております。本講演では、研究者・教育者としての取り組み、学長として取り組んだこと、そしてこらからについてお話させていただきます。 東北大において研究者として歩み始めた当初から、産学連携による研究推進は当たり前のように行いました。1980年代90年代、日本の半導体に勢いのあった時は、何をやっても楽し

published on

Prof. Hua Wang

ETH(スイス連邦工科大学チューリッヒ校)のHua Wang教授に講演いただきました。 Speaker: Prof. Hua Wang (ETH, Zurich, Swiss) Title: “Fundamentals of RF and mm-Wave Power Amplifier Designs” Abstract: This talk presents a focused overview of mm-wave power-amplifier (PA) designs in silicon, including design fundamentals, advanced PA architectures, and state-of-the-art design examples. As phased arrays and MIMO systems have become ubiquitous in various wireless communication and sensing applications, they pose a completely new level of system complexity and different and often tighter requirements on the wireless frontend electronics, in particular the PAs. The talk will start with an introduction of PA performance metrics and their impacts on wireless systems. Next, it presents the design fundamentals of PA active devices and passive networks as well as power combining strategies. The tutorial discusses advanced PA architectures, including Doherty, Outphasing, LMBA, and Coupler-Balun Doherty PAs, for high efficiency, linearity, and bandwidth. Further, advance and challenges of high mm-Wave PAs in large-scaled arrays will be covered to address various emerging wireless applications. Finally, the talk will conclude with several state-of-the-art mm-wave PA design examples.

published on

Top Contributors of A-SSCC 2005-2023受賞

松澤先生と岡田先生が、国際会議A-SSCCの2005-2023まで期間におけるTop Contributorに選出されました。

published on

EuMWでDバンド無線機のデモ

EuMW (European Microwave Week)で、Dバンド無線機のデモを行いました!!

published on

OB

NVIDIAで働いているOBが研究室に遊びに来てくれました!!

published on

OB/OG Party

5年ぶりにOB/OG会を開催しました! OB/OG MLが届いていない人は secretaryssc.pe.titech.ac.jp まで連絡ください!

published on

Prof. Patrick Mercier

カリフォルニア大学サンディエゴ校(UCSD)からのPatrick Mercier教授に東工大に訪問頂き、ご講演くださいました! Speaker: Prof. Patrick P. Mercier, University of California, San Diego (UCSD) Title: “Low-Power Standards-Compatible Wireless Communications Circuits for Next-Generation IoT and Wearable Applications” Abstract: Emerging Internet-of-Things (IoT) devices for use in smart homes, wearable systems, industrial monitoring, smart cities, and beyond all require robust yet low-power wireless communications. Unfortunately, most current wireless standards do not intrinsically support low-power operation due to strict requirements on modulation formats, data rates, linearity, packet overheads, and so on. These restrictions impose minimum power consumption requirements for cellular standards (e.g., GSM, LTE, and 5G) and WiFi, but also surprisingly limit the ability of supposedly low-power standards (e.g., Bluetooth Low Energy and Narrowband-IoT) from reaching new application-enabling power levels. This presentation will outline the major challenges facing power reduction in modern wireless systems, and will describe several possible solutions to these challenges. Specifically, we will explore the use of wake-up receivers as a means to reduce the power overhead of between-node synchronization. Then, we will discuss an alternative communication scheme that can help to reduce the power of communication in WiFi, BLE, and body-area-network systems by >1,000x through use of standards-compatible backscatter communication systems, including the latest developments incorporating retroreflection and beam steering. We will also discuss related sensing circuit opportunities to round out the application space.

published on

Hansさんの博士論文発表会

博士課程のHans HERDIANさんの博士論文発表会を開催しました!

published on

VLSI Symposiumで3件発表

IEEE Symposium on VLSI Technology & CircuitsでChenxin Liuさん、加藤さん、Yi Zhangさんが発表しました! Chenxin Liu “A 640-Gb/s 4x4-MIMO D-Band CMOS Transceiver Chipset” Sena Kato “A 28GHz 5G NR Wirelessly Powered Relay Transceiver Using Rectifier-Type 4th-Order Sub-Harmonic Mixer” Yi Zhang “A 28GHz 4-Stream Time-Division MIMO Phased-Array Receiver Utilizing Nyquist-Rate Fast Beam Switching for 5G and Beyond”

published on

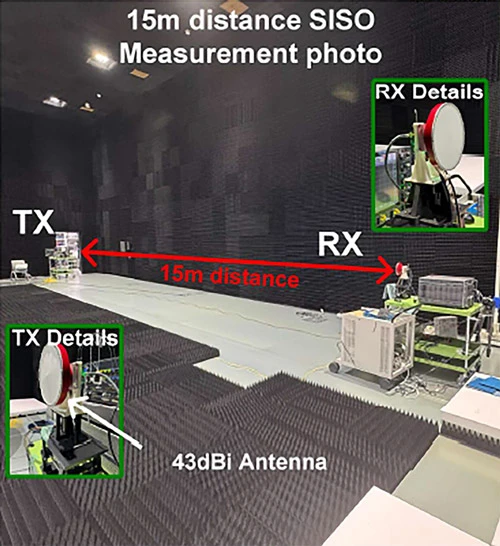

サブテラヘルツ帯CMOS ICで640Gbpsの無線伝送に成功

超高速無線通信を用いた遠隔医療や自動運転の実装に前進 要点 世界最速の640 Gbpsの伝送速度を達成するCMOS送受信ICを開発 次世代無線通信での周波数候補であるD帯(110-170 GHz)で動作 超高速通信を用いた新サービスの創出や次世代通信インフラへの応用を期待

published on

電子情報通信学会 論文賞

山崎 雄大さんが、電子情報通信学会 論文賞を受賞しました!

published on

BEST SEED AWARD

田 安宜(Anyi Tian)さんが東京工業大学 SSSマッチングワークショップでBEST SEED AWARDを受賞しました !!

published on

MCRG研究会

MCRG研究会を開催しました(2024/5/24)。 コロナ禍もあり、最後の対面開催が2020/1/16だったので、4年3か月ぶりでした。 5/24(Fri) 17:30-18:30 招待講演 @ S4-202 (S422) 環境社会理工学院 笠井 康子先生 「月に行ってテラヘルツ波で観測しよう! TSUKIMI: Lunar Terahertz SUrveyor for KIlometer-scale MappIng」 18:30- ポスターセッション @ S4-203 (S423) Zijie LIANG (Prof. Fukawa lab) Slotted Unsourced Random Access Using Massive MIMO over Frequency Selective Channels Kui WANG (Prof. Sakaguchi lab) Smart Mobility Digital Twin for Automated Driving Futo NODA (Prof. Tran lab) Proposal of LEO based Population Estimation System using Smartphone Emitted WLAN Signals Zhou DERUN (Prof. Takada lab) Prediction of Shadowing Loss of 2D Object by Mirror Kirchhoff Approximation with Unequal Interval Yaxiang WU (Prof. Hirokawa lab) Millimeter-Wave Slot Array Antennas using Gap Waveguides and Perpendicular Corporate-Feed Parallel Plates for Simplified Fabrication Chun WANG (Prof. Okada lab) 300GHz-band 4-Element Amplifier-Last Phased-Array Transmitter

published on

Prof. Wei Deng and Prof. Xiang Gao

清華大のWei Deng先生(SSCS DL)と浙江大学のXiang Gao先生が、東工大を訪問されました。 5/2(木) 15:30-16:30 Prof. Wei Deng (SSCS DL講演会) “Joint Radar-communication CMOS Transceiver” 16:30-17:30 Prof. Xiang Gao “Frac-N Sampling PLL with Phase Detection and Quantization Noise Cancellation in a Single Ramp Generation” ★各講演の詳細 (Talk 1) Speaker: Prof. Wei Deng (Tsinghua University) Title: Joint Radar-communication CMOS Transceiver: From System Architecture to Circuit Design Abstract: Recent years, millimeter-wave and Terahertz radar systems for sensing and radio systems for communication have attracted substantial attention both from the academia and industry. In addition, there is an increasing demanding for fusing both the hardware platform and frequency band of the radar and radio system, which has advantages of energy efficiency, performance optimization, spectrum sharing/efficiency, compact size, interference management, and the overall cost, as compared to assembling of two distinct systems. This lecture will introduce the current and future trends in the emerging joint radar-communication CMOS transceiver from system architecture to circuit design. Bio: Wei Deng received the B.S. and M.S. degrees from the University of Electronic Science and Technology of China (UESTC), China, in 2006 and 2009, respectively, and the Ph.D. degree from the Tokyo Institute of Technology, Japan, in 2013. He was with Apple Inc., Cupertino, CA, USA, working on RF, mm-wave, and mixed-signal IC design for wireless transceivers and Apple A-series processors. Currently he is with Tsinghua University, Beijing, China, as an Associate Professor. His research interests include RF, mm-wave, terahertz, and mixed-signal integrated circuits and systems for wireless communications, sensing, and imaging systems. He has authored or co-authored more than 160 IEEE journal and conference articles. Dr. Deng is a TPC Member of ISSCC, VLSI, A-SSCC, CICC and ESSCIRC. He has been an Associate Editor and a Guest Editor of the IEEE Solid-State Circuits Letters (SSC-L), a Guest Editor of the IEEE Journal of Solid-state Circuits (JSSC), and a Distinguished Lecturer of the IEEE Solid-State Circuits Society (SSCS). (Talk 2) Speaker: Prof. Xiang Gao (Zhejiang University) Title: Frac-N Sampling PLL with Phase Detection and Quantization Noise Cancellation in a Single Ramp Generation Abstract: Conventional PLLs detecting phase error in the time domain using a phase frequency detector often suffer from poor in-band phase noise due to the limited phase detector (PD) gain. The (Sub-)Sampling PLL is becoming a popular low jitter PLL architecture due to high gain of the SSPD. However, the high gain SSPD has a limited linear detection range, which is a challenge in fractional-N operation with the quantization noise. This talk presents a SPLL design with a merged constant-slope digital-to-time converter(DTC) and sampling phase detector (CSDTC-SPD). It realizes phase detection as well as quantization noise cancellation in a single ramp generation. Bio: Xiang Gao

published on

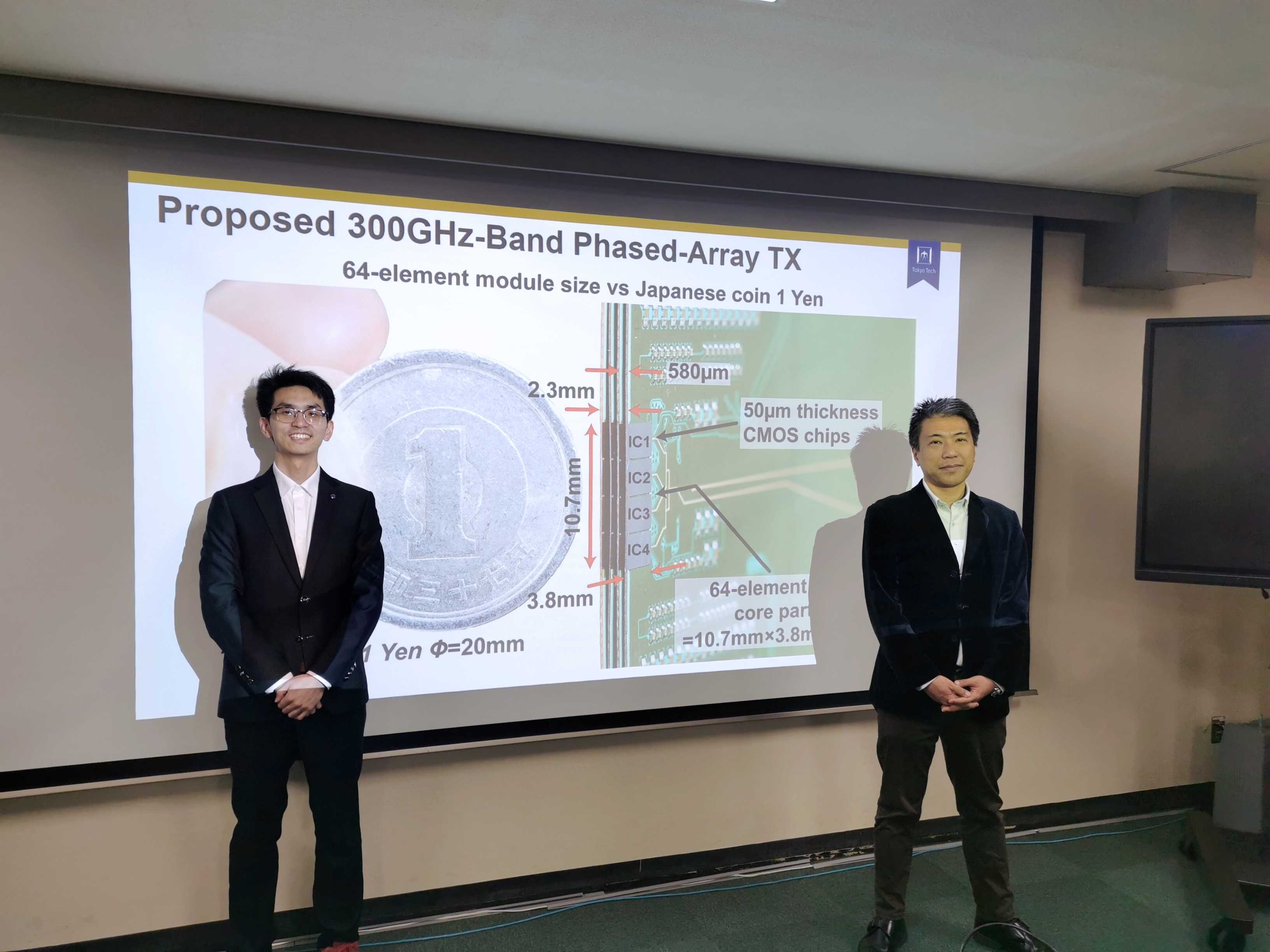

Wang Chunさんの博士論文発表会

博士課程のWang Chunさんの博士論文発表会を開催しました!

published on

お花見

洗足池でお花見しました!

published on