新着情報

電子情報通信学会 論文賞

山崎 雄大さんが、電子情報通信学会 論文賞を受賞しました!

BEST SEED AWARD

田 安宜(Anyi Tian)さんが東京工業大学 SSSマッチングワークショップでBEST SEED AWARDを受賞しました !!

MCRG研究会

MCRG研究会を開催しました(2024/5/24)。

コロナ禍もあり、最後の対面開催が2020/1/16だったので、4年3か月ぶりでした。

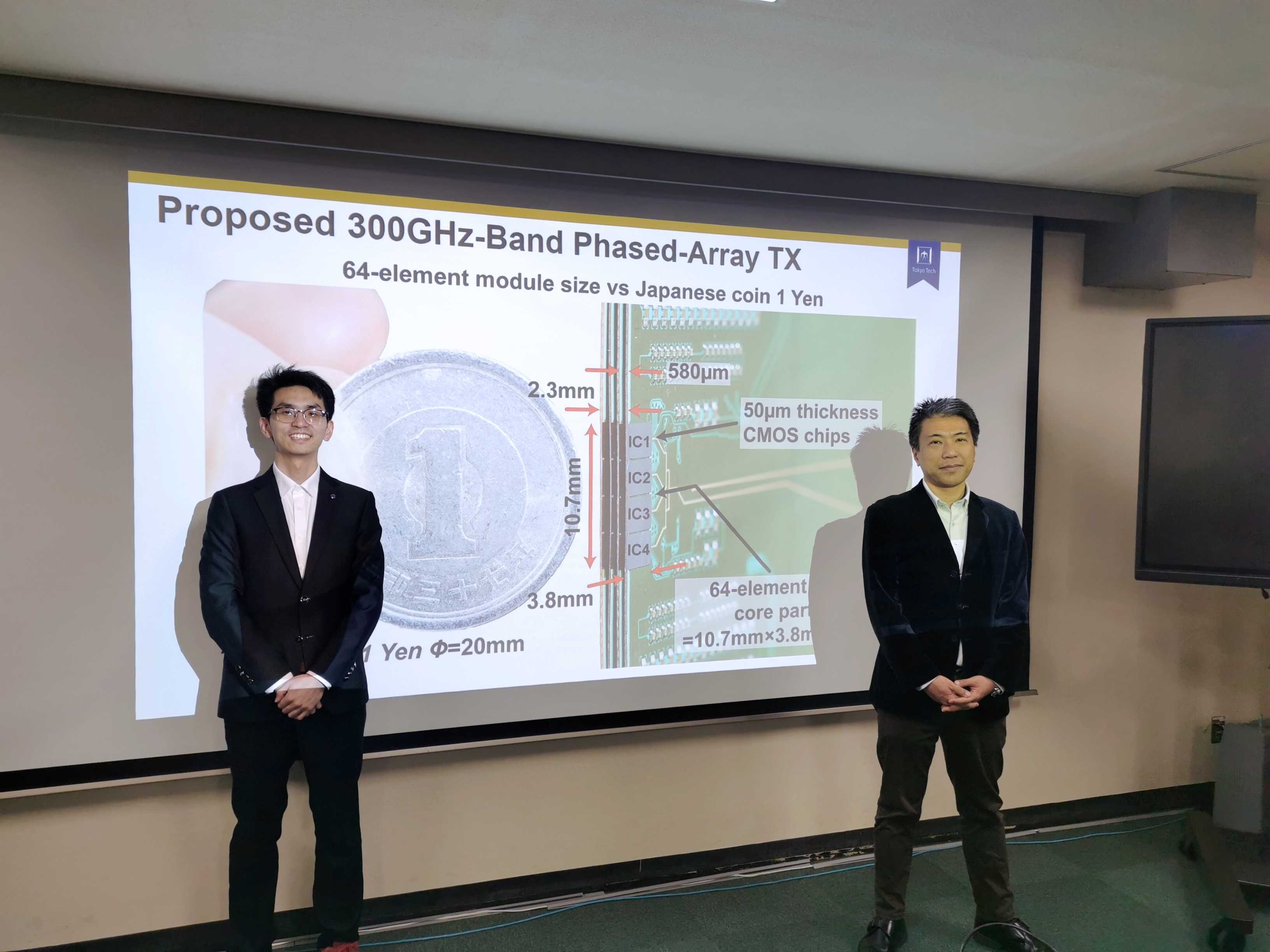

5/24(Fri) 17:30-18:30 招待講演 @ S4-202 (S422) 環境社会理工学院 笠井 康子先生 「月に行ってテラヘルツ波で観測しよう! TSUKIMI: Lunar Terahertz SUrveyor for KIlometer-scale MappIng」 18:30- ポスターセッション @ S4-203 (S423) Zijie LIANG (Prof. Fukawa lab) Slotted Unsourced Random Access Using Massive MIMO over Frequency Selective Channels Kui WANG (Prof. Sakaguchi lab) Smart Mobility Digital Twin for Automated Driving Futo NODA (Prof. Tran lab) Proposal of LEO based Population Estimation System using Smartphone Emitted WLAN Signals Zhou DERUN (Prof. Takada lab) Prediction of Shadowing Loss of 2D Object by Mirror Kirchhoff Approximation with Unequal Interval Yaxiang WU (Prof. Hirokawa lab) Millimeter-Wave Slot Array Antennas using Gap Waveguides and Perpendicular Corporate-Feed Parallel Plates for Simplified Fabrication Chun WANG (Prof. Okada lab) 300GHz-band 4-Element Amplifier-Last Phased-Array Transmitter

Prof. Wei Deng and Prof. Xiang Gao

清華大のWei Deng先生(SSCS DL)と浙江大学のXiang Gao先生が、東工大を訪問されました。

5/2(木) 15:30-16:30 Prof. Wei Deng (SSCS DL講演会)

“Joint Radar-communication CMOS Transceiver”

16:30-17:30 Prof. Xiang Gao

“Frac-N Sampling PLL with Phase Detection and Quantization Noise Cancellation in a Single Ramp Generation”

★各講演の詳細

(Talk 1) Speaker: Prof. Wei Deng (Tsinghua University)

Title: Joint Radar-communication CMOS Transceiver: From System Architecture to Circuit Design

Abstract: Recent years, millimeter-wave and Terahertz radar systems for sensing and radio systems for communication have attracted substantial attention both from the academia and industry. In addition, there is an increasing demanding for fusing both the hardware platform and frequency band of the radar and radio system, which has advantages of energy efficiency, performance optimization, spectrum sharing/efficiency, compact size, interference management, and the overall cost, as compared to assembling of two distinct systems. This lecture will introduce the current and future trends in the emerging joint radar-communication CMOS transceiver from system architecture to circuit design.

Bio: Wei Deng received the B.S. and M.S. degrees from the University of Electronic Science and Technology of China (UESTC), China, in 2006 and 2009, respectively, and the Ph.D. degree from the Tokyo Institute of Technology, Japan, in 2013. He was with Apple Inc., Cupertino, CA, USA, working on RF, mm-wave, and mixed-signal IC design for wireless transceivers and Apple A-series processors. Currently he is with Tsinghua University, Beijing, China, as an Associate Professor. His research interests include RF, mm-wave, terahertz, and mixed-signal integrated circuits and systems for wireless communications, sensing, and imaging systems. He has authored or co-authored more than 160 IEEE journal and conference articles. Dr. Deng is a TPC Member of ISSCC, VLSI, A-SSCC, CICC and ESSCIRC. He has been an Associate Editor and a Guest Editor of the IEEE Solid-State Circuits Letters (SSC-L), a Guest Editor of the IEEE Journal of Solid-state Circuits (JSSC), and a Distinguished Lecturer of the IEEE Solid-State Circuits Society (SSCS).

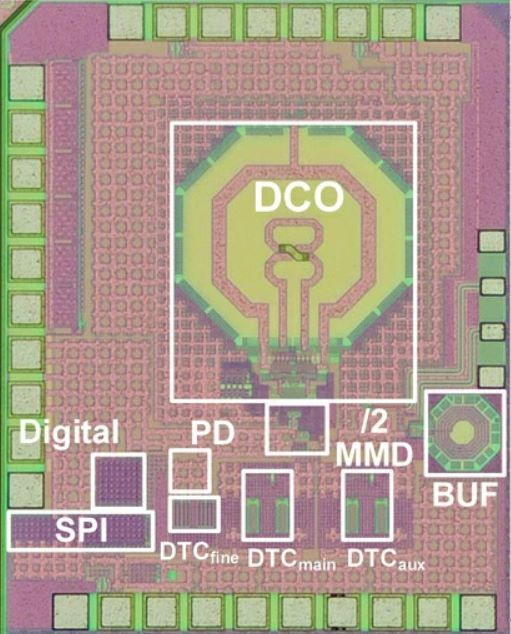

(Talk 2) Speaker: Prof. Xiang Gao (Zhejiang University)

Title: Frac-N Sampling PLL with Phase Detection and Quantization Noise Cancellation in a Single Ramp Generation

Abstract: Conventional PLLs detecting phase error in the time domain using a phase frequency detector often suffer from poor in-band phase noise due to the limited phase detector (PD) gain. The (Sub-)Sampling PLL is becoming a popular low jitter PLL architecture due to high gain of the SSPD. However, the high gain SSPD has a limited linear detection range, which is a challenge in fractional-N operation with the quantization noise. This talk presents a SPLL design with a merged constant-slope digital-to-time converter(DTC) and sampling phase detector (CSDTC-SPD). It realizes phase detection as well as quantization noise cancellation in a single ramp generation.

Bio: Xiang Gao received the B.E. degree from the Zhejiang University, Hangzhou, China, in 2004 and the M.Sc. and Ph.D. (cum laude) degrees from the University of Twente, Enschede, The Netherlands, in 2006 and 2010 respectively, both in electrical engineering. From 2010 to 2016, he was a principal engineer and design manager with Marvell Semiconductor, Santa Clara, CA, focusing on analog and RF IC design for wireless transceivers. From 2016 to 2018, he was an Engineering Director with Credo Semiconductor, Milpitas, CA, working on high-speed SerDes. Since August 2018, he has been a Faculty member at Institute of VLSI Design, Zhejiang University, China. He is an IEEE senior member, and TPC member of RFIC(2014-current)、CICC(2016-2023) and ISSCC(2015-2019, 2024-current).

Wang Chunさんの博士論文発表会

博士課程のWang Chunさんの博士論文発表会を開催しました!

お花見

洗足池でお花見しました!

Prof. Vadim Issakov

3/28に、IEEE MTT-S Japan/Kansai/Nagoya Chapterの主催で、DML講演会(Distinguished Microwave Lecture)が開催され、 ブラウンシュヴァイク工科大学(Technische Universität Braunschweig)のProf.Vadim Issakov先生に、ミリ波レーダーの研究についてご講演頂きました。

大学院入試説明会

大学院入試説明会が開催されます。研究室の見学もできますので、是非、現地参加ください!

第1回 2024年3月27日(水)13:00 - 17:00

第2回 2024年5月10日(金)13:00 - 17:00

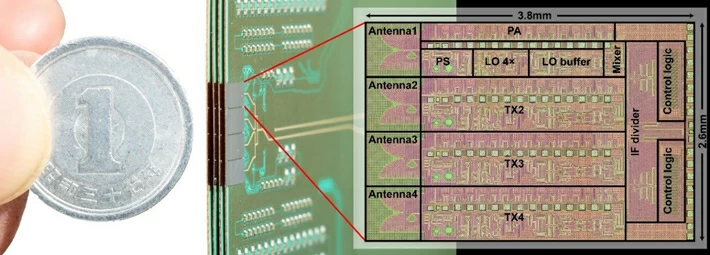

オールCMOSの300 GHz帯フェーズドアレイ送信機を開発

published onBeyond 5Gに向けた新規デジタル位相同期回路を開発

published onISSCC Student Research Preview (SRP) Poster Award

Dingxin Xuさんが、ISSCC 2023 Student Research Preview (SRP) Poster Awardを受賞しました!

ISSCC 2024で6件発表

ISSCC 2024で発表します!

Regular Session

- Dingxin Xu, et al.,“A 7GHz Digital PLL with Cascaded Fractional Divider and Pseudo-Differential DTC Achieving -62.1dBc Fractional Spur and 143.7fs Integrated Jitter”

- Chun Wang, et al.,“A 236-266GHz 4-Element Amplifier-Last Phased-Array Transmitter in 65nm CMOS”

Forum Presentation

- Kenichi Okada, “Low-Power Fractional-N Digital PLL Design Techniques”

湯浅景斗さん、Yi Zhangさん、Chenxin Liuさんが、Student Research Previewで発表します。

Prof. Vadim Issakov

11/21 ブラウンシュヴァイク工科大学(Technische Universität Braunschweig)のProf.Vadim Issakov先生が東工大に訪問され、最新の研究内容についてご講演頂きました.

昔の写真

講演資料を作っていたら出てきたので貼ってみます。。

松澤先生の古希とDonald O. Pederson賞、岡田先生のIEEE Fellow賞を祝う会

松澤先生の古希とDonald O. Pederson賞、岡田先生のIEEE Fellow昇格を記念して、祝賀会を開催しました!

研究室OB/OGやゲストの皆様含め90名以上の方々にご参加いただきました!

益学長

道正先生(初博士)

宮原先生(元助教)

本村先生

池田先生

山崎さん(博士学生)

打ち上げ

Chun Wangさん、Dinxin Xuさん、おめでとうございます!!

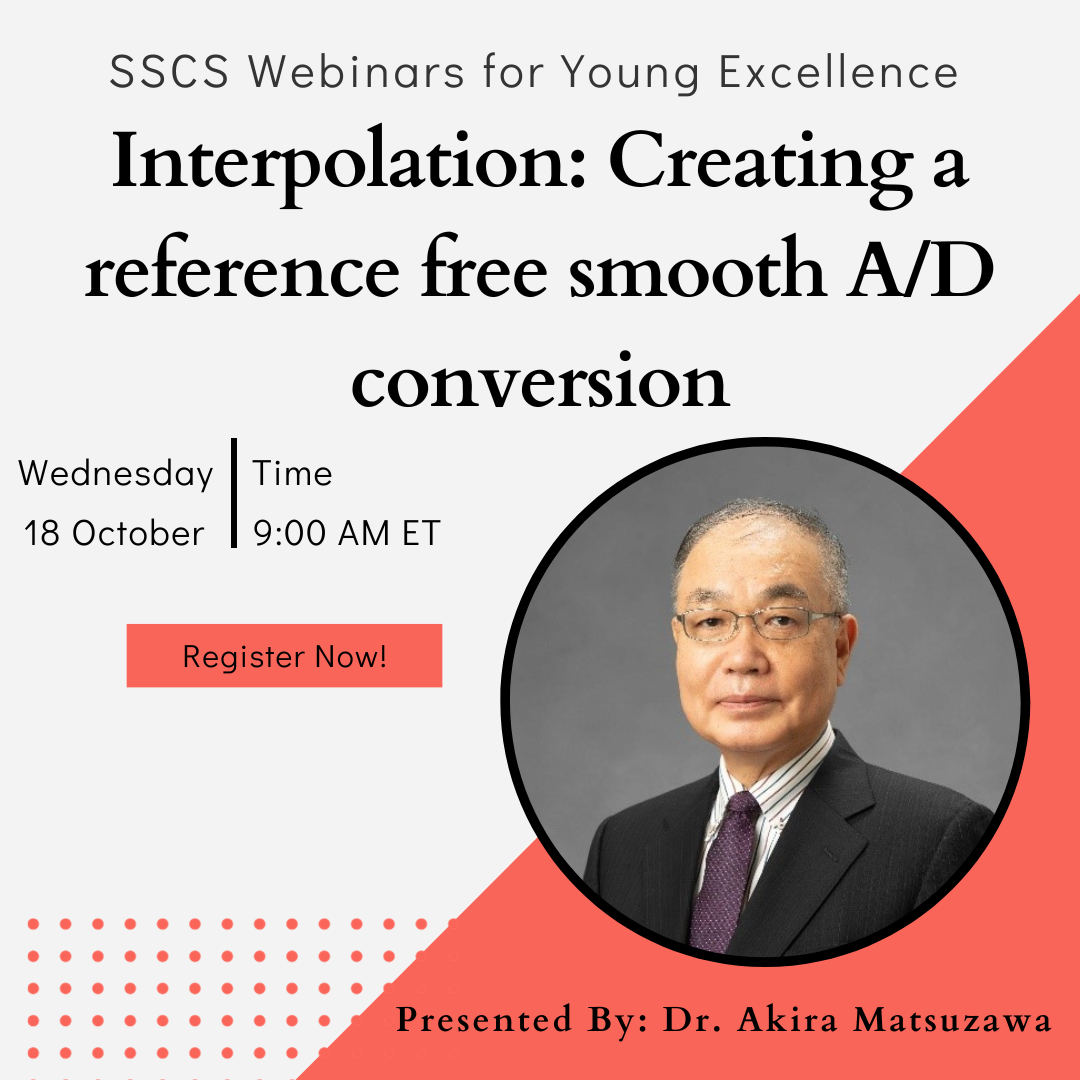

Webinar by 松澤先生

Title: Webinars for Young Excellence: Interpolation: Creating a reference free smooth A/D conversion

Presenter: Prof. Akira Matsuzawa

Abstract: Conventional A/D conversion is performed by comparing the input signal voltage with the reference voltage. On the other hand, by dividing and comparing the output voltages of two amplifiers with different reference voltages with the same input signal voltage, it was found that A/D conversion can be performed. This A/D conversion method is called interpolated A/D conversion.

This conversion method enables smooth A/D conversion with a small DNL without adjusting the gain of the amplifier or the reference voltage, and also enables low power consumption by reducing the number of amplifiers.

In this talk, we will introduce not only the principles and effects of interpolated A/D conversion, but also conceptual methods in circuit development, such as generalization by intuition and formulation that gave rise to unique A/D conversion methods.

A resistive-interpolated Bi-CMOS ADC was developed for home HDTV receivers. A capacitive-interpolated CMOS ADC reduced the power consumption to 1/8 of other ADCs was developed for the portable digital video equipment such as a handy camcorder. A gate-width interpolation CMOS ADC achieved ultra-high-speed operation of 400 MS/s and 1/10 the power consumption of the other ADCs. It is embedded on the world’s first one-chip Mixed Signal SoC for DVD and contributed higher performance and lower cost of DVD recorders.

In this talk, we would like you to understand that the interpolated A/D conversion method is not just an idea but was created for the development of A/D converters with high performance and low power in order to realize the new electronic devices.

Akira Matsuzawa received B.S., M.S., and Ph.D. degrees in EE from Tohoku University, Sendai, Japan, in 1976, 1978, and 1997. In 1978, he joined Panasonic, and in 2003, joined Tokyo Institute of Technology as a full professor, and in 2018, became professor emeritus and CEO of Tech Idea. He has been developing video-rate ADCs, mixed-signal SoCs and millimeter-wave CMOS transceivers. In 2022, he received IEEE Donald. O. Pederson award in Solid-State Circuits. He is an IEEE Fellow since 2002 and Life-Fellow since 2023.

ホームページリニューアル

ホームページをリニューアルしました。

Hugo+Static CMS+Github+Github Actionsで動いています。流行り?のSSG(Static Site Generation)にしてみました。

Decap CMS (旧Netlify CMS)は、最近v3になって日本語編集がまともになりましたが、結局、Static CMSにしてみました。

IEEE SSCS Japan Chapter VDEC Design Award

山崎さんがIEEE SSCS Japan Chapter VDEC Design Awardを受賞しました!

Prof. Inchan Ju

Prof. Inchan Ju先生に訪問いただきました!