# 位相補間回路の高精度化に関する検討

Consideration for Accurate Phase Interpolator

桂木 真希彦

タライル ナラヤナン アラビンド

岡田 健一

松澤 昭

Makihiko Katsuragi

Aravind Tharayil Narayanan

Kenichi Okada

Akira Matsuzawa

東京工業大学 大学院理工学研究科 電子物理工学専攻 Department of Physical Electronics, Tokyo Institute of Technology

### 1 まえがき

同一のハードウェアで様々な無線通信規格に対応できるソ フトウェア無線技術において、高い基準周波数を用いつつも 高分解能な周波数制御が可能な Fractional-N 型の PLL が広く 用いられている。従来は分周器の分周比を動的に切り替える ことにより分数分周を実現していたが、近年注目されている Sub-Sampling PLL においては分周器を用いない分数分周の実 現が求められている。

その実現方法の一つとして、位相補間回路を用いて VCO の 出力信号を多位相に分割し、参照信号との比較に使う位相を 順次切り替えることで分数分周を実現する方法がある[1]。こ の方法では位相補間回路の精度が PLL のジッタ性能に大きく 影響することから、本研究では位相補間回路の高精度化につ いて検討を行った。

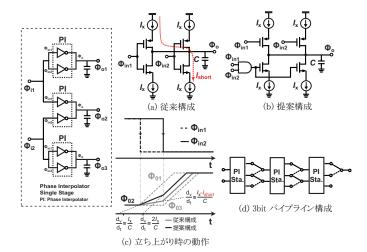

#### 2 従来構成

従来のインバータを用いた位相補間回路 [2] の構成を図 1 に 示す。位相の異なる  $\Phi_{i1}$ ,  $\Phi_{i2}$  を入力すると、各入力を反転さ せた  $\Phi_{\mathrm{ol}},\Phi_{\mathrm{o3}},$  およびその中間の位相  $\Phi_{\mathrm{o2}}$  を出力する。位相補 間回路は図 1(a) のような 2 つのインバータから構成されてお り、それぞれが電流  $I_x$  で出力端の容量 C に充放電を行う。

位相補間回路の立ち上がり時の動作を説明する。 $\Phi_{o1}, \Phi_{o3}$ はそれぞれ  $\Phi_{i1}$ ,  $\Phi_{i2}$  の立ち下がりの瞬間から  $\frac{dV}{dt} = \frac{2I_x}{C}$  の傾きで立ち上がる。一方、 $\Phi_{o2}$  は  $\Phi_{i1}$  の立ち下がりの瞬間から  $\frac{1}{C}=rac{I_{

m X}}{C}$ の傾きで立ち上がり始め、 $\Phi_{

m i2}$ の立ち下がりの瞬間から $\frac{1}{C}=rac{I_{

m X}}{C}$ の傾きで立ち上がり始め、 $\Phi_{

m i2}$ の立ち下がりの瞬間かん  $\frac{1}{C}$ ら  $\frac{dV}{dt} = \frac{2I_{\mathrm{x}}}{C}$  の傾きで立ち上がる。こうして  $\Phi_{\mathrm{o}2}$  は、 $\Phi_{\mathrm{o}1}$  と  $\Phi_{o3}$  の中間位相での立ち上がりを実現する。

しかし実際には図 1(c) のように、 $\Phi_{i1}$  の立ち下がりから, $\Phi_{i2}$ の立ち下がりまでの間、 $\Phi_{in1}$  側の PMOS と, $\Phi_{in2}$  側の NMOS が同時に ON になることにより貫通電流が流れる。これによっ て、電流 Ix が全て充電に使われず、位相補間の精度が劣化す る問題があった。

# 3 提案構成

提案構成を図 1(b) に示す。提案構成では、 $\Phi_{in1}$  と  $\Phi_{in2}$  が共 に High であるときのみ NMOS が ON になるように制御して いる。これによって、 $\Phi_{\mathrm{inl}}$  が立ち下がった瞬間に両側の NMOS が OFF になるため、貫通電流を防ぐことができる。

また、従来構成ではnビットの位相出力のために $2^{n-1}$ 個の 位相補間回路が必要であったが、図 1(d) のようなパイプライ ン型の構成 [3] を用いることで必要な回路ブロックを n 個まで 削減し、消費電力と面積の削減を実現した。

シミュレーション結果および性能比較は表1の通りである。

# 4 結論

位相補間回路において、従来の課題であった貫通電流を防 ぐような構成を提案した。これに加えて、パイプライン型の構 成を用いることで、高精度・低消費電力・小面積な位相補間回 路を実現した。

位相補間回路の構成と動作

表 1 位相補間回路の性能比較

|                         | This      | [4]       | [5]   | [3]          |

|-------------------------|-----------|-----------|-------|--------------|

| bits                    | 3         | 8         | 2     | 6            |

| Input Freq. [GHz]       | 0.5 - 3.0 | 0.1 - 1.5 | 0.3   | 0.025 - 0.25 |

| INL [LSB]               | < 0.5     | 1.33      | -     | 2.07         |

| DNL [LSB]               | < 0.6     | 0.5       | 1.06  | 0.91         |

| Power/Freq              | 0.53      | 2.9       | 0.038 | 0.12         |

| [mW/GHz]                |           |           |       |              |

| Area [mm <sup>2</sup> ] | 0.003     | 0.06      | -     | -            |

## 謝辞

本研究の一部は、総務省委託研究『電波資源拡大のための研究開 発』、総務省 SCOPE、半導体理工学研究センター、東工大基金、並び に東京大学大規模集積システム設計教育研究センターを通し、日本ケ イデンス株式会社、メンター株式会社の協力で行われたものである。

- [1] A. T. Narayanan, et al., "A Fractional-N Sub-Sampling PLL using a Pipelined Phase-Interpolator with an FoM of -246dBc/Hz," IEEE European Solid-State Circuits Conference, Sept. 2015.

- [2] B. W. Garlepp, et al., "A Portable Digital DLL for High-Speed CMOS Interface Circuits," IEEE Journal of Solid-State Circuits, May 1999.

- [3] S. Kumaki, et al., "A 0.5V 6-bit Scalable Phase Interpolator," IEEE Asia Pacific Conference on Circuits and Systems, Dec. 2010.

- [4] M. S. Chen, et al., "A 0.1-1.5 GHz 8-bit Inverter-Based Digital-to-Phase Converter Using Harmonic Rejection," IEEE Journal of Solid-State Circuits, Nov. 2013.

- [5] A. Nicholson, et al., "A 1.2V 2-bit phase interpolator for 65nm CMOS," IEEE International Symposium on Circuits and Systems, May 2012.