# 注入同期を利用した 自動合成配置配線可能な All Digital Synthesizable PLL

中田 憲吾, Deng Wei, Yang Dongsheng, 上野 智大, Narayanan Tharayil Aravind, Siriburanon Teerachot, 近藤 智史, 岡田 健一, 松澤 昭 東京工業大学 松澤・岡田研究室

# 1. 研究背景

#### PLL(位相同期回路)

従来アナログカスタム設計が必要

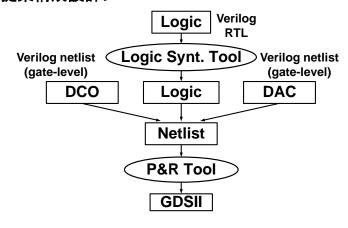

## Synthesiazble PLL

デジタル設計ツールのみで合成

- Digital design flow - スケーラビィリティ

- プロセス移植性

- 設計時間&コスト削減

# 課題:Layout uncertainty

Lavout

Verilog

- 😊 自動レイアウトによりTDC,DCOの線形性劣化 →TDCベースのPLLではジッタ劣化

- 従来手法 注入同期を利用したジッタの改善

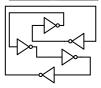

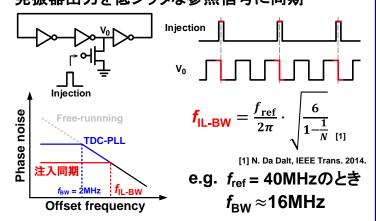

# 2. 注入同期PLL(IL-PLL)

·注入同期方式(Injection Lock) 発振器出力を低ジッタな参照信号に同期

○ 広い帯域によりジッタ改善可能かつ 自動レイアウトでのジッタ劣化を回避

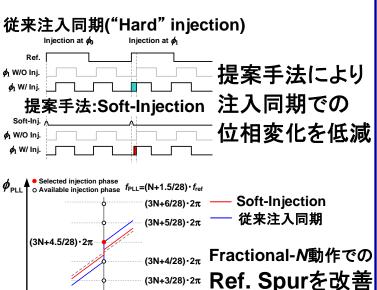

#### 3. 注入同期の課題

注入同期での大きな位相変化により

- ❷ Ref. Spur 大(従来:-40dBc)

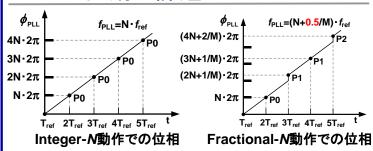

- ❷ Integer-N動作に限定

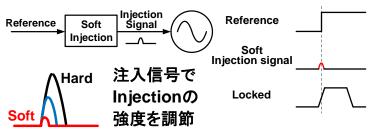

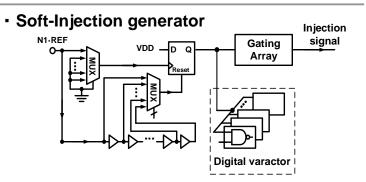

# 4. 提案手法:Soft-Injection

Soft-Injectionによる位相変化

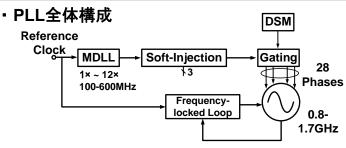

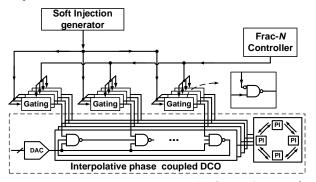

# 4. 提案回路構成

- カスケード構造により高い周波数で注入同期

- ・Multiphase DCOを用いたFractional-N動作

- Multiphase DCOにより28の位相に注入選択可能

- PI(Phase Interpolator)を利用し、各位相を補正

- 提案構成設計フロー

#### 5. 測定結果

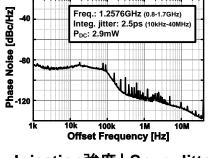

·Phase noise測定結果

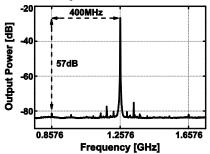

▪Ref. Spur測定結果

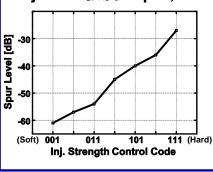

•Injection強度とSpur, Jitter

(Soft) 001 011 101 111 (Hard)

Inj. Strength Control Code

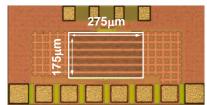

·Synthesizable PLL チップ写真

## •性能比較

|                    | This work                | [1]             | [2]             |

|--------------------|--------------------------|-----------------|-----------------|

| Technology         | 65nm                     | 65nm            | 65nm            |

| Power<br>[mW]      | <b>2.9</b><br>@1.2576GHz | 0.78<br>@0.9GHz | 13.7<br>@2.5GHz |

| Area [mm²]         | 0.048                    | 0.0066          | 0.04            |

| Integ. Jitter [ps] | 2.5                      | 1.7             | 3.2*            |

| FOM [dB]           | -227                     | -237            | -219*           |

| Topology           | Soft-IL                  | IL              | TDC-based       |

| Туре               | Frac-N                   | Integer-N       |                 |

| Synthesized?       | YES                      |                 |                 |

\*FOM is calculated based on RMS jitter.

[1] W. Deng, et al., ISSCC 2014 [2] Y. Park, et al., CICC 2011

#### 6. 結論

- 世界初Synthesizable PLLでFractional-N動作を実現した。

- Soft-Injectionにより、注入同期において、Ref. Spurを-57dBc(従来:-40dBc)

に抑えることが可能になった。

#### 謝辞

本研究の一部は、総務省委託研究『電波資源拡大のための研究開発』、総務省SCOPE、科学研究費補助金、半導体理工学研究センター、東工大基金、並びに東京大学大規模集積システム設計教育研究センターを通し、日本ケイデンス株式会社、シノプシス株式会社およびメンター株式会社の協力で行われたものである。