# Delta-Sigma Time to Digital Converter Using Charge Pump and SAR ADC

アヌゲラー フィルダウスィ 徐祖 楽 松澤 昭 宮原 正也 Anugerah Firdauzi Zule Xu Akira Matsuzawa Masaya Miyahara

東京工業大学 大学院理工学研究科 雷子物理工学専攻

Department of Physical Electronics, Tokyo Institute of Technology

### 1. Introduction

One of the straightforward methods for time to digital conversion is using time to charge conversion by using charge pump which is then connected to a SAR ADC for digital conversion [1]. The SAR ADC, while it is convenient for providing both charge storage and conversion, also provides high challenges for more than 10 bits resolution design while maintaining its speed high.

In this paper, lower-bit SAR ADC is used to obtain smaller area and lower power consumption. To overcome the resolution drop, delta-sigma ( $\Delta\Sigma$ ) structure using oversampling is used. Furthermore, the noise-shaping can also significantly reduce inband quantization noise from SAR ADC.

# 2. Circuit Design

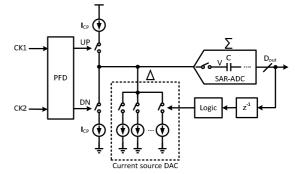

The architecture of the proposed  $\Delta\Sigma$  TDC is presented in Fig.1. In this architecture, a charge-pump is used to convert the time difference input,  $T_{IN}$ , into charge which is then stored in the SAR CDAC. Between each conversion, ideally the charge stored in SAR CDAC is constant, thus by never resetting the SAR, the charge stored on each conversion cycle is accumulated and an integrator ( $\Sigma$ ) can be obtained.

To implement the  $\Delta$ , SAR ADC quantization output is used as selector for the current source DAC to discharge/charge SAR CDAC in a constant time interval,  $T_{DAC}$ , for positive/negative output in the next conversion cycle. In this way, a first order  $\Delta\Sigma$ TDC with SAR ADC as quantizer can be implemented.

In  $\Delta\Sigma$  system, integrator input needs to be kept close to zero by making feedback DAC in the same level with the input. For the case of this TDC, maximum charge from the input must be equal with total charge from the feedback, or  $max(T_{IN})$ .  $I_{CP} =$  $T_{DAC}$ .  $\Sigma I_{DAC}$ , where  $I_{CP}$  is the charge pump current and  $\Sigma I_{DAC}$  is the total current from current source DAC.

Multibit quantization using 4 bit SAR ADC is used in this structure to improve the first order  $\Delta\Sigma$  TDC's resolution by 1-1.5 bit for every quantization bit increase. Higher resolution SAR ADC is not required since the resolution in  $\Delta\Sigma$  modulator is determined mostly by the oversampling rate (OSR) and filter/integrator order. In this way, the design of SAR ADC can be kept simple, fast, and low power. Faster SAR ADC will allow the use of higher OSR and doubling the OSR can improve the resolution by 1.5 bit.

## 3. Simulation Results

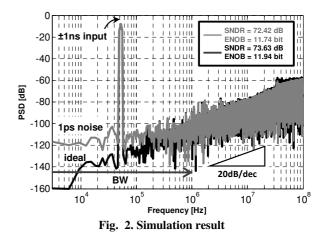

The proposed structure was simulated by using MATLAB with ±1ns full-scale input difference at 52 kHz, 1 MHz bandwidth, OSR=100, for ideal condition and with 1 ps charge-pump noise.

Fig. 1. Delta-sigma TDC architecture

As presented in Fig.2, the simulation results shows 20 dB/dec noise shaping, and the noise floor became higher when the noise is applied. Both simulation results give SNDR higher than 72 dB, and ENOB more than 11 bit, or less than 0.9 ps effective resolution.

#### 4. Conclusion

A new approach for TDC by using  $\Delta\Sigma$  architecture with charge domain analysis is proposed. The  $\Delta\Sigma$  TDC implemented by using charge-pump, SAR ADC, and current source DAC gives first order noise shaping and high resolution for moderate bandwidth while keeping the input range large and power consumption low.

#### Acknowledgment

This work was partially supported by HUAWEI, Berkeley Design Automation for the use of the Analog FastSPICE(AFS) Platform, and VDEC in collaboration with Cadence Design Systems, Inc.

#### References

[1] Z. Xu, S. Lee, M. Miyahara, and A. Matsuzawa, "A 0.84ps-LSB 2.47mW time-to-digital converter using charge pump and SAR-ADC", IEEE Custom Integrated Circuits Conference (CICC) 2013