# Class-C型電圧制御発振器に おける適応バイアス回路の 低雑音化の検討

〇中田憲吾, 木村健将, 竹内康揚 岡田健一, 松澤昭 東京工業大学大学院理工学研究科

#### 発表内容

TOKYO TECH

Pursuing Excellence

- 研究背景

- ・ 従来型Class-C VCOの特徴

- 提案するClass-C VCO

- シミュレーションによる検証

- 結論

ΤΠΚΥΠ

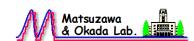

60GHz 局部発振器の要求性能

Phase Noise: -95 dBc/Hz @1MHz Offset (57~66GHz)

20GHz 発振器の要求性能

Phase Noise: -105 dBc/Hz @1MHz Offset (19~22GHz)

$PN_{ILO} = PN_{VCO} + 20log_{10}N \quad (N=3)$

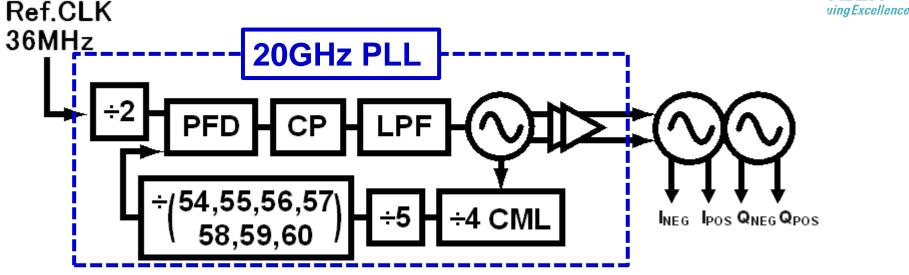

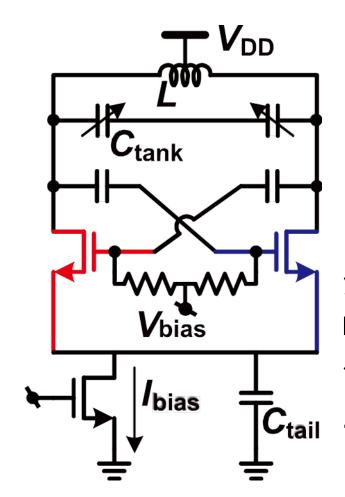

# Class-C VCO 従来回路[1]

Vbiasに固定電圧を与え、 Vbiasを低い電圧に設定する。

- ☺ 良好な位相雑音特性

- ♡ 低消費電力化が可能

[1] A. Mazzanti, et al., JSSC 2008

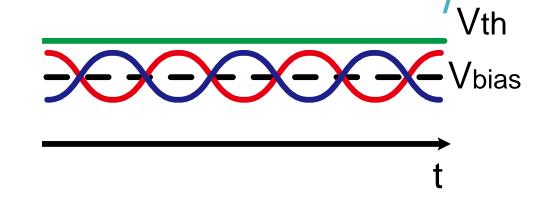

#### Class-C VCO[1] におけるStartup Problem

発振開始時にVbiasを低くしすぎると振幅が小さいために、ゲート電圧がしきい値電圧Vthを上回らず、トランジスタが上手く導通しない。

安定した発振が得られなくなる。

6

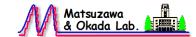

[3] L. Fanori, et al., ESSCIRC 2012

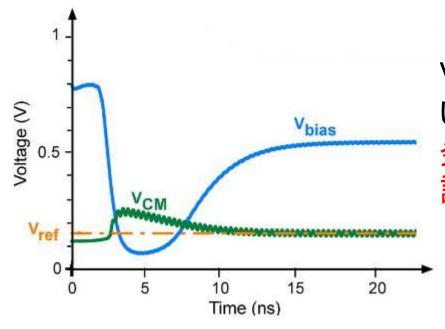

VbiasはVcmとVrefの差動出力としているため、発振開始時は高く、そして発振安定後は発振開始時よりも低く設定できる。

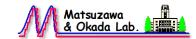

- 良好な位相雑音特性

- ◎ 低消費電力化が可能

- 🙁 オペアンプによりノイズも同時に増幅

- ⊗ ノイズ成分遮断には時定数の大きなRCフィルタが必要

#### 提案回路

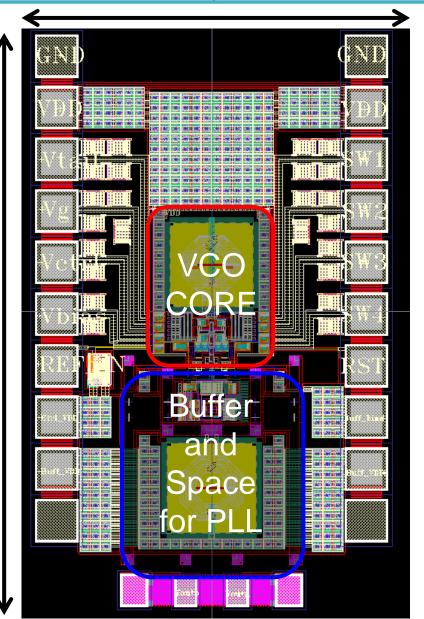

1100µm

Technology: CMOS 65nm Core Area:

$0.069 \text{mm}^2$

**Buffer:**

Pout: 0~1 [dBm]

Power: 3.2 [mW]

#### 従来回路[1]と提案回路の性能比較

|                     | 提案回路    | 従来回路[1]     |         |

|---------------------|---------|-------------|---------|

| Topology            | Class-C | Class-C(※1) | Class-B |

| Vbias[V]            | 0.45    | 0.58        | 0.58    |

| PN@1MHz<br>[dBc/Hz] | -106.5  | -102.5      | -106.4  |

| Power[mW]           | 8.3     | 5.4         | 9.4     |

| FoM[dBc/Hz]         | -183.9  | -181.2      | -182.9  |

Class-C動作では提案回路の方が位相雑音を4.0[dBc/Hz]改善できる。またClass-B動作では、消費電力を1.1[mW]削減できる。

結果的に従来回路[1]よりもFoMを改善することができる。

(※1) Class-C動作のためクロスカップルトランジスタのサイズを変えている。

#### 従来回路[2]と提案回路の性能比較

|                              | 提案回路    | 従来回路[2] |               |

|------------------------------|---------|---------|---------------|

| Topology                     | Class-C | Class-C |               |

| 制御回路面積<br>[mm <sup>2</sup> ] | 0.004   | 0.018   | 0.004<br>(※2) |

| Ratio to VCO<br>CORE [%]     | 5.8     | 26.1    | 5.8           |

| PN@1MHz<br>[dBc/Hz]          | -106.6  | -106    | -98.97        |

| Power[mW]                    | 7.8     | 7.9     | 7.8           |

| FoM[dBc/Hz]                  | -183.9  | -183.3  | -176.2        |

(※2) 従来回路[2]の制御回路面積を提案回路と同じ面積で再現した場合の性能比較(RCフィルタを小さくした場合)

### 従来回路[2]と提案回路の性能比較

従来回路[2]ではオペアンプによって増幅されたノイズを遮断するために、RCフィルタを用いており、RCフィルタには十分大きな値のR,Cを用いる必要がある。→結果的に回路面積が大きくなる。

#### 提案回路の利点

- ・低位相雑音を実現する場合、従来回路[2]よりもVCO coreに占める制御回路面積の割合を20%削減することができる。

- 提案回路と同じ面積の従来回路[2]を考えた場合に、位相雑音を比較すると提案回路の方が低位相雑音を実現することができる。

提案回路はより小さな面積で低位相雑音を実現できる。

- 今回、提案する回路はClass-C VCOにDACおよび制御回路を挿入したものであり、この方法では、発振の安定性を確保しつつ、位相雑音を-106 [dBc/Hz] (@1MHz Offset)以下の性能で実現できることを確認した。

- 制御回路については従来回路[2]よりも回路全体に 占める面積の割合を20%削減しつつ、上記の低位 相雑音が実現できることを確認した。

## Thank you for your attention.

#### PVT(Process Voltage Temperature)耐性の検討

従来回路[1]は製造ばらつきにより、しきい値電圧が高くなった場合を考慮すると、安定した発振を確保するために、Vbiasを0.58Vに設定する必要があった。

一方、提案回路においては発振開始時を0.58Vに設定し、発振が安定するのに伴い、0.45Vまで下げることができると確認した。

→提案回路では最終的にVbiasを0.58Vから0.45V まで下げられるため、消費電力1.5[mW]の削減に つながっている。