# 60 GHz 帯全4チャネル対応低消費電力 CMOS 無線送信回路

A 60 GHz Full-4ch Low-Power CMOS Integrated Direct-Conversion Transmitter

| 浅田 大樹 | 南 亮 | 津久井 祐基 | 山口 達也 | アハマドムサ | 佐藤 高洋 | Hiroki Asada | Ryo Minami | Yuki Tsukui | Tatsuya Yamaguchi | Ahmed Musa | Takahiro Sato

Yasuaki Takeuchi Kenichi Okada Akira Matsuzawa

## 東京工業大学 大学院理工学研究科 電子物理工学専攻

Department of Physical Electronics, Tokyo Institute of Technology

#### 1 まえがき

近年、CMOS プロセスを用いた 60 GHz 帯無線通信回路の研究が盛んに行われている。無線通信システムをすべてオンチップで作り上げることによって、省コストでの製造と小型化が可能となる。本研究では CMOS 65 nm プロセスを用いてフル差動構成のダイレクトコンバージョン型 60 GHz 帯無線送信回路の試作を行った。

#### 2 回路構成

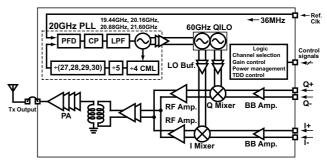

図 1 に送信回路のブロック図を示す。消費電力と面積の観点からダイレクトコンバージョン方式を採用している [1]。送信回路は4段電力増幅器、IQ2つのミキサー、60GHz注入同期型直交局部発振器から構成されている。

コモンソース型電力増幅器は伝送線路を用いて整合回路を構成している。また短冊状の MIM キャパシタを並べた配線を低インピーダンスな伝送線路としてモデリングした MIM TLをデカップリングとして用いている。ミキサーにはギルバートセル型ダブルバランストミキサーを採用しており、出力はキャパシティブクロスカップル [2] を用いた差動増幅器によって増幅された後にバランで単相信号に変換され、電力増幅器に入力される。キャパシティブクロスカップルによって安定性と改善し、高電力利得との両立を実現している。

局所発振器は 20 GHz PLL と 60 GHz 注入同期型直交局部発振器から成っている [3]。注入同期型直交局部発振器は三逓倍器として働き、20 GHz PLL からの入力とテールの IQ カップリングによって 60 GHz 直交位相信号を発生させる。

また回路各部のバイアス電圧はデジタルアナログ変換器によって供給され、外部からのデジタル的な回路制御が可能である。

#### 3 測定結果

全ての回路は一枚のチップに集積されており、アンテナと共にパッケージングされている。測定の結果、変換利得は 18 dB、飽和出力電力は 5.6 dBm であった。また送信回路全体を通した最終的な位相雑音は 1 MHz 離調時に全てのチャネルで-95 dBc/Hz以下であることを確認した。消費電力は QPSK 変調を用いる際は 150 mW、16QAM 変調を用いる際は 257 mW であった。

図 2 にコンスタレーションとスペクトラムを示す。 IEEE802.15.3c の規格に則った全てのチャネルでの通信を BER が  $10^{-3}$  以下の条件で実現した。この測定では任意波形発生器を用いて変調信号を送信し、オシロスコープを用いて EVM と BER の評価を行った。帯域幅は IEEE802.15.3c の規格より 2.16 GHz、シンボルレートは 1.76 Gs/s、ロールオフ率は 25 %である。測定の結果、EVM は QPSK 変調で-21.4 dB、16QAM 変調で-23.3 dB を確認した。通信距離は QPSK 変調では 1.6 m 以上、16QAM 変調では 0.5 m 以上である。 いずれもチャネル 3の測定結果であり、中心周波数は 62.64 GHz である。またより広い帯域を用いることで QPSK で 8 Gb/s、16QAM で 10 Gb/s の通信が可能であることを確認した。

図 1 送信回路のブロック図

| Constellation                         | * *                                                            | 16. 数使用<br>18. 数 单 38<br>36. 数 单 38<br>36. 数 卷 48               | 光器 产业<br>最 件 件 选<br>身 妆 去 垛<br>车 查 每 查                        |

|---------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------|---------------------------------------------------------------|

| Spectrum                              | 10<br>0<br>-10<br>-20<br>-30<br>-40<br>59.40<br>62.64<br>65.88 | 10<br>0<br>-10<br>-20<br>-30<br>-40<br>-59,40<br>62,64<br>65,88 | 10<br>0<br>-10<br>-20<br>-30<br>40<br>59.40<br>62.64<br>65.88 |

| Modulation                            | QPSK                                                           | 16QAM                                                           | 16QAM                                                         |

| Data rate<br>(BER <10 <sup>-3</sup> ) | 3.52Gb/s                                                       | 7.04Gb/s                                                        | 10.0Gb/s                                                      |

| EVM(with DFE)                         | -21.4dB                                                        | -23.3dB                                                         | -23.0dB                                                       |

| Power<br>Consumption                  | 150mW(Tx)<br>104mW(Rx)                                         | 257mW(Tx)<br>162mW(Rx)                                          | 257mW(Tx)<br>162mW(Rx)                                        |

| Distance                              | 1.6m                                                           | 0.5m                                                            | 0.01m                                                         |

図 2 コンスタレーションとスペクトラム (チャネル 3)

#### **4** まとめ

$60\,\mathrm{GHz}$  帯無線送信回路の試作を行い、通信規格に則った全てのチャネルで通信が可能なことを確認した。またより広い帯域を用いて QPSK で  $8\,\mathrm{Gb/s}$ 、 $16\,\mathrm{QAM}$  で  $10\,\mathrm{Gb/s}$  の通信を達成した。

#### 謝辞

本研究の一部は、総務省委託研究『電波資源拡大のための研究開発』、総務省 SCOPE、科学研究費補助金、半導体理工学研究センター、NEDO、キヤノン財団、並びに東京大学大規模集積システム設計教育研究センターを通し、日本ケイデンス株式会社およびアジレント・テクノロジー株式会社の協力で行われたものである。

### 参考文献

- K. Okada, et al., "A Full 4-Channel 6.3 Gb/s 60 GHz Direct-Conversion Transceiver With Low-Power Analog and Digital Baseband Circuitary,", ISSCC, Feb. 2012.

- [2] Wei L. Chan, et al., "A 60GHz-Band 1V 11.5dBm Power Amplifier with 11% PAE in 65nm CMOS", ISSCC, Feb. 2009.

- [3] A. Musa, et al., "A 58-63.6GHz quadrature PLL frequency synthesizer in 65nm CMOS," A-SSCC Dig. Tech. Papers, pp.189-192, Nov. 2010.