### ソフトウェア無線へ向けた CMOS マルチバンド送受信機の研究

- Research of a Multi-band Transceiver for Software Defined Radio -

伊藤 利彦<sup>†</sup> 金丸 正樹<sup>†</sup> 今西 大輔<sup>†</sup> 洪 芝英<sup>†</sup> 古谷 聡<sup>†</sup> Dong Tangoc Huy<sup>†</sup> 岡田 健一<sup>†</sup> 松澤 昭<sup>†</sup>

†東京工業大学大学院理工学研究科電子物理工学専攻 〒152-8552 東京都目黒区大岡山 2-12-1-S3-27 E-mail: †itot@ssc.pe.titech.ac.jp

**あらまし** 近年の無線通信技術の発達によって端末のサイズやコスト、消費電力が増大しており、これに対処するためにソフトウェア無線の実現が求められている。我々の研究グループでは、ソフトウェア無線を実現するために欠かすことのできないマルチバンド送受信機の実現を目指し、チューナブルノッチフィルタを用いた高線形受信機や、スイッチを用いた広帯域電力増幅器(PA)を CMOS チップで試作し、検討を行った。

キーワード SDR, 受信機, 電力増幅器

#### 1. はじめに

#### 1.1. ソフトウェア無線

近年の無線通信技術の発達に伴い、様々な民生用のアプリケーションが開発されてきた。現在の無線通信ではそれぞれの通信規格に対応する複数の RFIC が必要となるため、チップ面積や消費電力、製造コストが増大してしまう。この状況を改善するため、ソフトウェア無線(SDR)が提案されている[1]。また、SDR の具体的な回路構成に関しては[2]で提案されている。SDRを実現するためには、全ての周波数に対応したマルチバンド送受信機が必要となる。

#### 1.2. 受信機

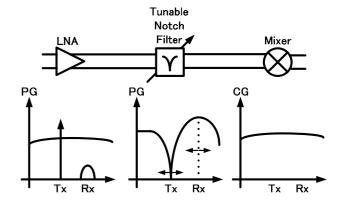

マルチバンド受信機の実現のために大きな問題と なるのが、WCDMA 受信機等で発生する送信波リーク という現象である。従来の受信機では、妨害波除去の ために外付けの SAW フィルタを用いていたが、これ は周波数の可変性に乏しいため除去する必要がある。 そのため、マルチバンド受信機の実現のためには SAW フィルタを使用することなく送信波リークに対処する 技術が必要不可欠である。[3]では、フィードフォワー ドキャンセルという手法が提案されている。また、オ ンチップフィルタを用いた受信機が[4]で提案されて いる。[3]や[4]では高い線形性が実現されているが、そ れぞれの周波数に受信機が必要となる。[5]では、フィ ルタ等を用いずに低雑音増幅器や周波数混合器の線形 性を高めるという手法が用いられている。しかし、線 形性の大幅な改善は困難であると思われる。本論文で は、図 1 のような受信機を提案する。広帯域 LNA と Mixer、さらにその段間にチューナブルノッチフィルタ が接続されている。このフィルタによって送信波リー クの影響を軽減する。

#### 1.3. 電力増幅器

現在の携帯電話向けの電力増幅器には化合物半導

表 1 要求性能

|       | Gain    | Noise   | IIP3  | IIP2  |

|-------|---------|---------|-------|-------|

| LNA   | 18-23dB | 3dB     | 0dBm  | -     |

| Mixer | 12-15dB | 9nV/√Hz | 12dBm | 75dBm |

図1 受信機アーキテクチャ

体が使用されているが、他の RF 回路やデジタル回路との集積化のために CMOS で電力増幅器を実現しようとする研究が盛んに行われている。しかし、 CMOS トランジスタは微細化によって速度を向上してきた反反 所圧の劣化も同時に進んでいる。耐圧の低い CMOS トランジスタでは、出力マッチング回路において大きな利力となる。本語では、CMOS プロセスを押い、複数の周波数に対すったとは、CMOS プロセスを用い、複数の周波数に対すったとの電力増幅器を提案する。一方は抵抗フィードル回路規模増大の原因となる。もう一方の電力増幅器である。もう一方の電力増幅器である。もう一方の電力増幅器である。セカマッチングにオンチップトランスを用いることで

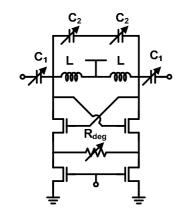

図 2 ノッチフィルタの回路図

(a) 容量アレイ

(b) ディジェネレーション用抵抗図3 容量と抵抗の詳細

広い周波数帯に対応し、高い出力電力と効率を実現した。

# 2. チューナブルフィルタを用いた受信機

#### 2.1. 線形性

WCDMA 等の FDD システムを採用している通信では、受信機側に漏れ出した送信信号が CW ブロッカと共に受信帯域に 3 次歪を発生させる。この歪は送信波リークの 2 乗に比例して大きくなる。送信波リークはデュプレクサのアイソレーションに依存するが、LNAの入力端で-30dBm 以上もの大きさになる。表 1 にマルチバンド LNA と Mixer に求められる性能を示す[6]。ダブルバランスドミキサーのような高い IIP2 を実現するものでも、ばらつきの影響で 40-50dBm 程度が限界であり、Mixer への要求性能がとても厳しいことが分かる。本論文では、ノッチフィルタを用いることでこの問題に対処する。

図4 LNAの回路図

図 5 Mixer の回路図

図 6 受信機のチップ写真

LNAによる歪を無視すると、受信機の IIP3 は以下のように表すことができる。

$$IIP3_{\text{wofilter}} = \frac{P_{\text{in}} + G_{\text{Rx}} - P_{\text{IM3,Mixer}}}{2} + P_{\text{in}}$$

(1)

ここで、 $G_{Rx}$  は LNA と Mixer のゲイン、 $P_{IM3,Mixer}$  は 3 次歪の出力電力である。ノッチフィルタが送信波リークを  $G_{sup,Tx}$  [dB]抑圧する場合、3 次歪は 2  $G_{sup,Tx}$  [dB] 小さくなる。そのため、ノッチフィルタを挿入した場合の受信機の IIP3 は以下のように計算できる。

$$IIP3_{\text{wifilter}} = \frac{P_{\text{in}} + \left(G_{\text{Rx}} - G_{\text{loss,Rx}}\right) - \left(P_{\text{IM3,Mixer}} - 2G_{\text{sup,Tx}}\right)}{2} + P_{\text{in}} (2)$$

ここで、 $G_{loss,Rx}$  はノッチフィルタの受信帯域のロスである。式(2)は  $IIP3_{wofilter}$  を用いて以下のように表すこ

図7 受信機のゲイン

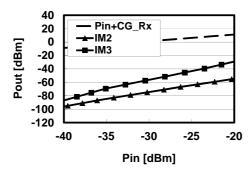

図 8 0.8GHz における出力と歪

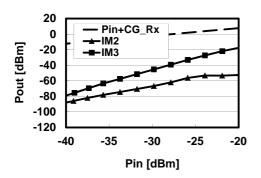

図 9 1.5GHz における出力と歪

とができる。

$$IIP3_{\text{wifilter}} = IIP3_{\text{wofilter}} + \left(G_{\text{sup,Tx}} - \frac{G_{\text{loss,Rx}}}{2}\right)$$

(3)

式(3)より、ノッチフィルタを挿入することで受信機の線形性が改善可能なことが分かる。

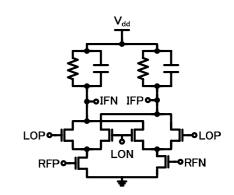

#### 2.2. ノッチフィルタ

図 2 にチューナブルノッチフィルタの回路図を示す。このフィルタは LC の直列・並列共振器と Q エンハンサで構成されている。共振器のインピーダンスは以下の式で表すことができる。

$$Z_N = j \frac{\omega(C_1 + C_2) - 1/\omega L}{\omega C_1 (1/\omega L - \omega C_2)}$$

(4)

式(4)より、ゼロとポールの周波数はそれぞれ以下の

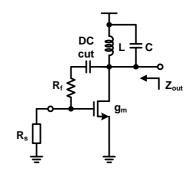

図 10 抵抗フィードバック型増幅器

図 11 抵抗帰還型 PA の回路図

図 12 抵抗帰還型 PA のチップ写真

ように計算できる。

$$f_{\text{zero}} = 1/2\pi\sqrt{L(C_1 + C_2)}$$

(5)

$$f_{\text{pole}} = 1/2\pi\sqrt{LC_2} \tag{6}$$

ゼロ点では全ての信号が反射し、ポールでは全ての信号が通過する。これらの周波数を調節することで、送 信波リークのみを減衰させることができる。

広いチューニングレンジを実現するために、共振器 [4,7]は図 3(a)に示すようにバラクタとスイッチトキャパシタで構成されている。Q エンハンサではトランジ

表 2 受信機の性能比較

|            | [4]         | [9]    | [10]   | [11]   | [12]       | This V    | Vork       |

|------------|-------------|--------|--------|--------|------------|-----------|------------|

| Freq.[GHz] | 2.1/1.9/0.8 | 2.1    | 2.1    | 2.1    | 1.8        | 0.8       | 1.5        |

| NF[dB]     | 2.8         | 3.1    | 5.5    | 4.9    | 2.9        | 6*        | 6.2*       |

| Gain[dB]   | 102         | 30     | 30.5   | 96.5   | 37         | 31        | 28         |

| IIP3[dBm]  | -2          | -12    | 5.3    | -7.4   | -7         | -1        | -4         |

| IIP2[dBm]  | 65          | >39    | 58     | >38.8  | 63         | >45       | >37        |

| Pdc[mW]    | 101.5-175   | 12     | 33.6   | 83.7   | 75         | 121       | 114        |

| Band       | Multi-band  | Narrow | Narrow | Narrow | Multi-band | Tunable&M | lulti-band |

<sup>\*</sup>simulation

スタをクロスカップルさせることで負性抵抗を作り出している。また、フィルタ自身の線形性を向上させるためにトランジスタのソース部分に図 3(b)に示されるディジェネレーション用の抵抗を接続した。この抵抗値はスイッチによって調整することが可能で、共振器の Q 値はテール電流によってチューニングできる。

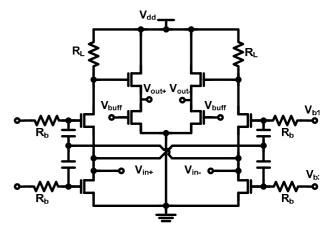

#### 2.3. LNA & Mixer

図 4 に LNA の回路図を示す。この LNA にはキャパシティブクロスカップル[8]とソースフォロアのバッファが使用されている。キャパシティブクロスカップルによって入力のコモンゲートトランジスタのノイズを一部キャンセルしている。また、出力のソースフォロアによって高い電力利得を実現し、後段のフィルタや Mixer のノイズの影響を小さくしている。

図 5 に広帯域 Mixer の回路図を示す。高い IIP2 を実現するためにダブルバランスドギルバートセルを採用した。出力部分の RC フィルタによってローパス特性を実現しており、カットオフ周波数は 10MHz で設計した。

#### 2.4. 測定結果

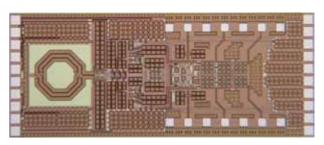

図 6 に受信機のチップ写真を示す。 $0.18\mu m$  CMOS プロセスで設計し、面積は  $2.5mm^2$  であった。電源電圧は 1.8V で、測定時は RF プローブと外付けの DC ブロック、アテネータを使用した。

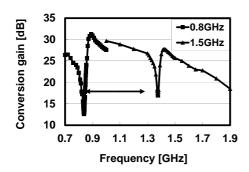

図7に0.8GHz と1.5GHz におけるコンバージョンゲインの測定結果を示す。ポールとゼロ周波数をスイッチトキャパシタやバラクタを用いて調整した。ノッチ周波数とパスバンドのゲインの差は0.8GHz 帯で18dB、1.5GHz 帯で10dB であった。差動信号の生成にはハイブリッドカプラを使用し、図の測定結果は測定装置の口スを校正した値である。

図 8,9 に 0.8 GHz,1.5 GHz 帯それぞれについて入力電力に対する出力電力、IM3、IM2 の測定結果を示す。 測定時は送信周波数をゼロに、受信周波数をポールに合わせた。測定の結果、0.8 GHz において IIP2 は 4 チップ測定して 45 dBm 以上、IIP3 は-1 dBm であった。

NF のシミュレーション結果は帯域内において 6-6.2dBで、受信機全体の消費電力は121mWであった。 表 2 に近年発表された SAW フィルタレスの受信機の 性能比較を示す。

## 3. 抵抗帰還型チューナブル電力増幅器

#### 3.1. 出力整合

アイソレータは無線送信機における主要な外付け 部品の一つであり、電力増幅器とデュプレクサの間に 接続される。アイソレータはアンテナのインピーダン スミスマッチによって生じる反射波から電力増幅器を 保護し、デュプレクサから送信機側を見たインピーダ ンスを 50Ωにし、デュプレクサを安定動作させるとい う役目を担っている。しかし、マルチバンド送信機を 実現する場合外付けかつ周波数の可変性に乏しいアイ ソレータは複数個必要となるため、回路規模を増大さ せてしまう。アイソレータを取り除くためには先程の アイソレータの役割から、反射波に対して堅牢で、出 カインピーダンスが広帯域で 50Ωにマッチング可能な 電力増幅器が必要となる。ここで、前者に関しては[13] において CMOS パワーアンプのドレイン端におけるピ ーク電圧を検出し、反射波が生じたら即座にパワーア ンプのゲインを下げる方法が提案されている。そこで、 本論文では後者の広帯域で 50Ωにマッチングを取る方 法を提案する。

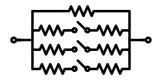

抵抗フィードバックは広い帯域で  $50\Omega$ に整合が取れる[14]手法で、LNA の入力に使用することが多い。図 10 に抵抗フィードバック型増幅器の回路図を示す。図 10 においてトランジスタのドレイン抵抗が十分に大きいと仮定すると、出力インピーダンス  $Z_{out}$  は以下のように表すことができる。

$$Z_{\text{out}} = \frac{R_{\text{f}} + R_{\text{s}}}{g_{\text{m}}R_{\text{s}} + 1} / / \frac{1}{j\omega C} / / (R_{\text{L}} + j\omega L)$$

(5)

ここで、R<sub>L</sub> はインダクタの寄生抵抗である。LC 共振 周波数において式(5)は以下のように計算できる。

$$Z_{\text{out}} = \frac{R_{\text{f}} + R_{\text{s}}}{g_{\text{m}}R_{\text{s}} + 1} // R_{\text{p}}$$

(6)

$$R_{\rm p} = \frac{L}{CR_{\rm I}} \tag{7}$$

ここで、 $R_p$  は LC の共振インピーダンスである。これらの式から、 $Z_{out}$  は  $R_f$  と C を調節することで任意の周波数で  $50\Omega$ にマッチング可能であることが分かる。

図 13 S22 の測定結果

図 14 S21 の測定結果

図 15 出力電力とゲイン、PAE

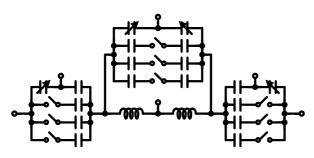

#### 3.2. 提案回路

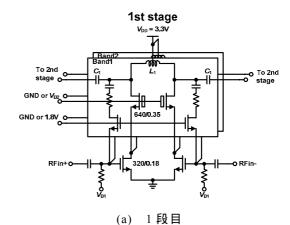

図 11 に提案する電力増幅器の回路図を示す。式(5) の計算ではトランジスタのドレイン抵抗は十分大きいと仮定していたが、実際は無視できるほど大きくないため、トランジスタをカスコードにすることでドレイン抵抗を増加させた。また、高電圧で使用可能な厚い酸化膜を持つトランジスタを使用し、電源電圧には3.3Vを使用している。出力電力を大きくするために差動で設計しており、抵抗と容量をスイッチで切り替え

図 16 4 つのバンドの性能

2nd stage

VDD = 3.3V

4560/0.35

From 1st stage

GND or V<sub>ES</sub>

GND or V<sub>ES</sub>

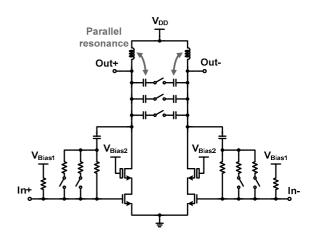

図 17 段間マッチング型 PA の回路図

2 段目

(a)

ることにより 4 つの周波数帯において出力整合を取る ことが可能である。

#### 3.3. 測定結果

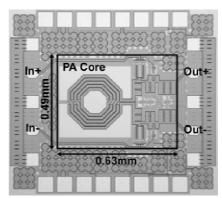

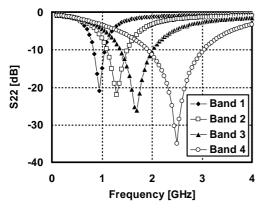

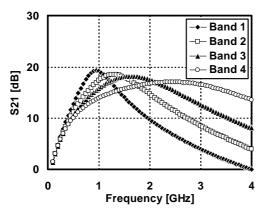

図 12 にチップ写真を示す。0.18μmCMOS プロセス で設計し、面積は 0.63 × 0. 49mm<sup>2</sup> であった。図 13,14

図 18 段間マッチング型 PA のチップ写真

図 19 S21 の測定結果

図 20 P<sub>sat</sub>、P<sub>1dB</sub>、PAE<sub>MAX</sub>の測定結果

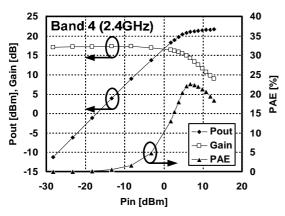

に各周波数帯における S22 と S21 の測定結果を示す。スイッチの切り替えにより 0.9-3GHz 間において出力整合を取ることが可能である。全帯域において S22<-10dB かつ S21>16dB を実現している。図 15 に 2.4GHz における入力電力に対する出力電力、ゲイン、PAE を示す。 $P_{SAT}$  は 21.7dBm、 $P_{1dB}$  は 18.6dBm、 $P_{AE_{MAX}}$  は 23%であった。4 つのパンドにおける  $P_{SAT}$ 、 $P_{1dB}$ 、 $P_{AE_{MAX}}$ を図 16 に示す。表 3 に CMOS プロセスを使用した電力増幅器の性能比較を示す。

## 4. 段間マッチング切り替え型電力増幅器

#### 4.1. インピーダンス変換

電力増幅器の最大出力電力は  $V_{\rm DD}^2/2R_{\rm L}$  で表される。そのため出力電力を大きくするには電源電圧を大きくするか、負荷抵抗を小さくする必要がある。前者に関しては CMOS プロセスの微細化に反する方法であり、望ましくない。そのため、大きな出力電力を得るためには出力マッチング回路を用いたインピーダンスとしては、LC回路では、両方をではである。LC回路では、両方をではバラクタを用いるものがある。LC回路では、ただ、C はバラクタを用いるという方法であるが、L を可変にすると通常大きなロスが発生してあるが、L を可変にすると通常大きなロスが発生ングの路を使用することが高効率、大電力な電力増幅器を実現するためには必要であると思われる。

#### 4.2. 提案回路

図 17 に提案回路を示す。大きなゲインを得るため に2段のアンプで構成され、出力にトランスが接続さ れている。その際、1段目と2段目の間でインピーダ ンスが複素共役になっていないと1段目から出力され た電力が十分に2段目に伝わらない。その場合、電力 増幅器全体のゲインコンプレッションが 1 段目で発生 してしまう。1段目のサイズを大きくすればこの問題 は解決できるが、1段目の消費電力が増加して PAE が 劣化してしまう。そこで、本論文では1段目、2段目 を共にカスコードにし、さらに1段目のゲート接地ト ランジスタと2段目のソース接地トランジスタをバン ド数分用意することによって、使用するバンドのトラ ンジスタのみバイアスをかけ、電流を流すことができ る構成にした。電力の反射を防ぐために段間のトラン ジスタを使用する周波数帯に応じてスイッチで切り替 え、広帯域なマッチングを実現している。

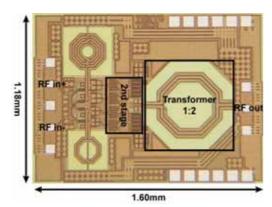

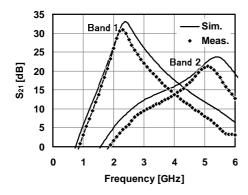

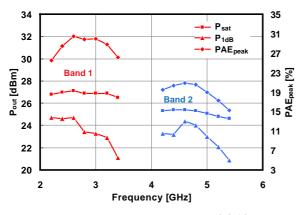

### 4.3. 測定結果

図 18 にチップ写真を示す。帰還抵抗型電力増幅器と同様に厚膜トランジスタを用いた  $0.18\mu m CMOS$  プロセスで設計しており、面積は  $1.18\times1.6mm^2$  である。図 19 に S21 のシミュレーションと測定結果を示す。 2 つのバンド両方において 20dB 以上のゲインが得られているが、測定時におけるゲインの減少や周波数の低下が確認できる。これは、トランスの電磁界シミュレーションと実際の測定値のずれや配線のインダクタンス成分を寄生抽出していないこと、寄生抽出の精度の影響等が主な問題だと思われる。図 20 にそれぞれのバンドにおける  $P_{SAT}$  と  $P_{1dB}$ 、 $PAE_{MAX}$  を示す。全周波数帯において 25dBm 以上の  $P_{SAT}$ 、21dBm 以上の  $P_{1dB}$ 、 $15%以上の <math>PAE_{MAX}$  を実現した。表 4 に性能比較を示す。

表 3 電力増幅器の性能比較(1)

|                                          | [15]     | [16]     | [17]     | [18]     | This Work(1) |

|------------------------------------------|----------|----------|----------|----------|--------------|

| CMOS Technology [nm]                     | 130      | 180      | 130      | 130      | 180          |

| $V_{\mathrm{DD}}\left[\mathrm{V}\right]$ | 1.5      | 2.8      | 3        | 1.5      | 3.3          |

| Frequency [GHz]                          | 0.5-5    | 3.7-8.8  | 1-2.5    | 2.4/3.5  | 0.9-3        |

| P <sub>1dB</sub> [dBm]                   | 10-18    | 14-16    | -        | -        | 17-21        |

| P <sub>sat</sub> [dBm]                   | 14-21    | 16-19    | 28-31    | 19       | 20-21        |

| $PAE_{MAX}[mW]$                          | 3-16*    | 8-25     | 18-43    | 43       | 11-23        |

| Area [mm <sup>2</sup> ]                  | 3.6      | 2.8      | 2.56     | 1.3      | 0.31         |

| S22 [dB]                                 | <-6      | <-8      | -        | <-15     | <-10         |

| Output Matching                          | Wideband | Wideband | Wideband | Dualband | Tunable      |

<sup>\*</sup>DE:Drain Efficiency

#### 5. まとめ

本論文では、チューナブルノッチフィルタを用いた マルチバンド受信機と、スイッチを用いた広帯域電力 増幅器を提案した。

受信機では、世界初のチューナブルノッチフィルタを用いた高線形受信機を実現した。フィルタは 49%のチューニングレンジを達成している。測定の結果 31dB のゲイン、45dBm の IIP2、-1dBm の IIP3 の測定結果を得た。

抵抗帰還型電力増幅器に関しては、アイソレータレスのマルチバンド送信機に向けて、広帯域に  $50\Omega$ にチューニングが可能な出力を実現した。測定の結果、全帯域において 20dBm 以上の  $P_{SAT}$ 、17dBm 以上 の  $P_{1dB}$ 、15%以上の PAE を達成した。世界初の可変出力インピーダンスを持つ CMOS 電力増幅器である。

段間マッチング切り替え型電力増幅器ではオンチップのトランスを用いることで出力電力が大きく、高効率な電力増幅器を実現した。また、ロスの少ない段間マッチングの切り替え技術を提案し、マルチバンドの電力増幅器を実現した。測定の結果、全周波数帯において 25 dBm 以上の  $P_{SAT}$ 、21 dBm 以上の  $P_{1dB}$ 、15%以上の  $P_{AE}$  を実現した。

#### 謝辞

本研究の一部は、総務省 SCOPE、半導体理工学研究センター、科学研究費補助金、NEDO、並びに東京大学大規模集積システム設計教育研究センターを通し、日本ケイデンス株式会社およびアジレント・テクノロジー株式会社の協力で行われたものである。

#### 文 献

- [1] J. Mitra, "The software radio architecture," IEEE Communications Magazine, vol.33, no. 5, pp.26-38, May 1995.

- [2] A. Abidi, "The Path to the Software-Defined Radio Receiver," IEEE Journal of Solid-State Circuits, vol. 42, no. 5, pp. 954-966, May 2007.

- [3] H. Darabi, "A blocker filtering technique for SAW-less wireless receivers," IEEE Journal of

- Solid-State Circuits, vol. 42, no. 12, pp. 2766-2773, Dec. 2007.

- [4] B. Tenbroek, J. Strange, D. Nalbantis, C. Jones, P. Fowers, S. Brett, C. Beghein, and F. Beffa, "Single-Chip Tri-Band WCDMA/HSDPA Transceiver without External SAW Filters and with Integrated TX Power Control," in IEEE International Solid-State Circuits Conference Digest of Technical Papers, 2008, pp. 202–203.

- [5] V. Giannini, P. Nuzzo, C. Soens, K. Vengattaramane, M. Steyaert, J. Ryckaert, M. Goffioul, B. Debaillie, J. V. Driessche, J. Craninckx, and M. Ingels, "A 2mm2 0.1-to-5GHz SDR Receiver in 45nm Digital CMOS," in IEEE International Solid-State Circuits Conference Digest of Technical Papers, 2009, pp. 408-409.

- [6] M. Brandolini, P. Rossi, D. Manstretta, and F. Svelto, "Toward multistandard mobile terminals-fully integrated receivers requirements and architectures," IEEE Transactions on Microwave Theory and Techniques, vol. 53, no. 3 Part 2, pp. 1026-1038, Mar. 2005.

- [7] H. Samavati, H. Rategh, and T. Lee, "A 5-GHz CMOS wireless LAN receiver frontend," IEEE Journal of Solid-State Circuits, vol. 35, no. 5, pp. 765-772, May 2000.

- [8] A. Amer, E. Hegazi, and H. Ragai, "A Low-Power Wideband CMOS LNA for WiMAX," IEEE Transactions on Circuits and Systems II, vol. 54, no. 1, pp. 4-8, Jan. 2000.

- [9] Y. Feng, G. Takemura, S. Kawaguchi, and P. Kinget, "Design of a High Performance 2-GHz Direct-Conversion Front-End With a Single-Ended RF Input in 0.13μm CMOS", IEEE Journal of Solid-State Circuits, vol. 44, No.5, pp1380-1390, May 2009.

- [10] E. Keehr and A. Hajimiri, "Equalization of IM3 Products in Wideband Direct Conversion Receivers," in IEEE International Solid-State Circuits Conference Digest of Technical Papers, 2008, pp. 204-607.

- [11] M. Tamura, T. Nakayama, Y. Hino, A. Yoshizawa, and K. Takagi, "A Fully Integrated Inter-Stage-Bandpass-Filter-Less Direct- Conversion Receiver for WCDMA," IEEE RFIC Symposium, 2005, pp.269-272.

- [12] N. K. Yanduru, D. Griffith, S. Bhagavatheeswaran, C.-C. Chen, F. Dulger, S.-J. Fang, Y.-C. Ho, and K. M. Low, "A WCDMA, GSM/GPRS/EDGE Receiver Front End without Interstage SAW Filter," IEEE RFIC Symposium, 2006, pp. 19-22.

表 4 電力増幅器の性能比較(2)

|                                         | [15]  | [17]  | [18]    | [19]  | This Work(2)    |

|-----------------------------------------|-------|-------|---------|-------|-----------------|

| CMOS Technology [nm]                    | 130   | 130   | 130     | 180   | 180             |

| $V_{\mathrm{DD}}\left[\mathrm{V} ight]$ | 1.5   | 3     | 1.5     | 3.3   | 3.3             |

| Frequency [GHz]                         | 0.5-5 | 1-2.5 | 2.4/3.5 | 2.1-6 | 2.2-3.4/4.2-5.4 |

| $P_{1dB}[dBm]$                          | 10-17 | -     | -       | 15-18 | 21-25           |

| P <sub>sat</sub> [dBm]                  | 14-21 | 28-31 | 19      | 18-22 | 25-27           |

| PAE <sub>MAX</sub> [mW]                 | 3-16* | 18-43 | 43      | 9-17  | 15-30           |

| Area [mm <sup>2</sup> ]                 | 3.6   | 2.56  | 1.3     | 0.97  | 1.89            |

<sup>\*</sup>DE:Drain Efficiency

- [13] F. Carrara, C. D. Presti, A. Scuderi, C. Santagati, and G. Palmisano, "A Methodology for Fast VSWR Protection Implemented in a Monolithic 3-W 55% PAE RF CMOS Power Amplifier," IEEE J. Solid-State Circuits, vol. 43, no. 9, pp. 2057-2066, Sep. 2008.

- [14] C. W. Kim, M. S. Kang, P. T. Anh, H. T. Kim, and S. G. Lee, "An Ultra-Wideband CMOS Low Noise Amplifier for 3-5-GHz UWB System," IEEE J. Solid-State Circuits, vol. 40, no. 2, pp. 544-547, Feb. 2005.

- [15] J. Roderick and H. Hashemi, "A 0.13μm CMOS Power Amplifier with Ultra-Wide Instantaneous Bandwidth for Imaging Applications," IEEE ISSCC Dig. Tech. Papers, pp. 374-375, Feb. 2009.

- [16] C. Lu, A.-V. H. Pham, M. Shaw, and C. Saint, "Linearization of CMOS Broadband Power Amplifiers Through Combined Multigated Transistors and Capacitance Compensation," IEEE Trans. Microw. Theory Tech., vol. 55, no. 11, pp. 2320-2328, Nov. 2007.

- [17] S. Kousai and A. Hajimiri, —An Octave-Range Watt-Level, Fully-Integrated CMOS Switching Power Mixer Array for Linearization and Back-Off-Efficiency Improvement, IEEE J. Solid-State Circuits, vol. 44, no. 12, pp. 3376-3392, Dec. 2009.

- [18] M. Ghajar, et al., "Concurrent Dual Band 2.4/3.5 GHz Fully Integrated Power Amplifier in 0.13mm CMOS Technology," IEEE European Microw. Conf., pp. 1728-1731, Sep. 2009.

- [19] D. Imanishi, et al., "A 2-6 GHz Fully Integrated Tunable CMOS Power Amplifier for Multi-Standard Transmitters," IEEE Asia and South Pacific Design Automation Conference, pp. 351-352, Feb. 2010.