# 60 GHz 帯 CMOS 低雑音増幅器における 位相差を考慮した3次歪みキャンセル

A 60 GHz CMOS Low Noise Amplifier Using IM3 Cancel Technique

瀬尾 有輝 南 亮 岡田 健一 松澤 昭 Yuki Seo Ryo Minami Kenichi Okada Akira Matsuzawa

> 東京工業大学 大学院理工学研究科 電子物理工学専攻 Department of Physical Electronics, Tokyo Institute of Technology

## 1 まえがき

受信機に用いられる低雑音増幅器 (LNA) の設計において、雑音指数と同様に、3次相互変調歪み (IM<sub>3</sub>) が非常に重要である。3次歪みがバイアス電圧に依存することを利用し、3次歪みを改善する回路が提案されている[1]。トラジスタを並列に繋げ、それぞれのゲート電圧を調整し、IM<sub>3</sub>成分が正負で打ち消しあうように設定することで、3次歪みの改善を行う。しかし、周波数が高くなると、3次歪みの位相成分がバイアス依存するため、うまく打ち消すことができない。本発表では、バイアス電圧の調整と位相差を補償するための伝送線路長の両者の調整により、60 GHz 帯でも3次歪みのキャンセルが行えるかをシミュレーションにより検討したので、それを報告する。

# 2 回路構成

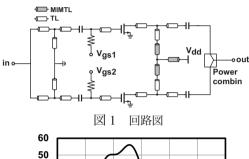

図1に、チャネル幅  $60 \, \mu m$  のトランジスタを並列に接続したときの LNA の回路図を示す。それぞれのゲートバイアス電圧を変化させることで一方のトランジスタによる  $3 \, \chi$ 歪みをもう一方のトラジスタの  $3 \, \chi$ 歪みによりキャンセルする。伝送線路によりマッチングブロックを構成した。 $60 \, \text{GHz}$  においては、両トランジスタ間の距離が無視できないため、それぞれの入出力に別々にマッチングブロックを設けた。それぞれの経路の出力を $100 \, \Omega$  にマッチングさせ、パワーコンバイナにより合成し最終的に  $50 \, \Omega$  にマッチングさせる。

#### 3 シミュレーション結果

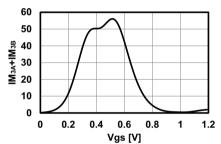

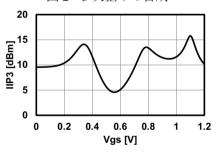

図 2 および図 3 にシミュレーション結果を示す。65nm CMOS の素子パラメータを用いた。片側の  $V_{gs}$  を 0.6 V に固定し、もう一方の  $V_{gs}$  を変化させた。3 次歪みは、入力 3 次インターセプトポイント  $IIP_3$  により評価した。図 2 は、それぞれの経路における 3 次歪み成分  $IM_3$  を、位相も考慮して足しあわせたものである。この値が低いほうが  $IIP_3$  が高くなる。図 2 の  $IM_3$  の和が減少すると、図 3 の  $IIP_3$  が増加する。完全に対応していないのは、利得もバイアス依存しているためである。図 3 のバイアス電圧の低い領域  $(V_{gs}=0.35$  V) で高い  $IIP_3$  が得られた。この際、位相差がちょうど 180 度となるように、伝送線路長で調整した。 $V_{gs}=0.35$  V の条件では、必要な伝送線路長は 260  $\mu$ m であった。

図2 3次歪みの合成

図3 IIP3

### 4 まとめ

60 GHz 帯低雑音増幅器の線形性改善のため、バイアス差をつけて3次歪みをキャンセルする手法において、位相差のバイアス依存に着目した。位相差を伝送線路で調整することにより、60 GHz 帯のおいても3次歪みをキャンセルが可能であることを示した。

## 謝辞

本研究の一部は、総務省委託研究『電波資源拡大のための研究開発』、総務省 SCOPE、科学研究費補助金、半導体理工学研究センター、NEDO、キヤノン財団、並びに東京大学大規模集積システム設計教育研究センターを通し、日本ケイデンス株式会社およびアジレント・テクノロジー株式会社の協力で行われたものである。

#### 参考文献

V. Aparin and L. E. Larson, "Modified derivative superposition method for linearizing FET low-noise amplifiers," *IEEE Trans. on Mi*crowave Theory and Techniques, Vol. 53, No. 2, pp. 571-581, Feb. 2005.