# リング発振器用低雑音電流源の検討

### A Low Noise Current Source for Ring Oscillators

韓 政勲\*

岡田 健一"

松澤 昭\*\*

Jeonghoon Han

Kenichi Okada\*\*

Akira Matsuzawa\*\*

東京工業大学大学院理工学研究科国際開発工学専攻、電子物理工学専攻が

Department of International Development Engineering', Department of Physical Electronics', Tokyo Institute of Technology

### 1 はじめに

LC 共振器を用いないリング発振器は広い周波数範囲を持つ一方、位相雑音の劣化という問題がある。特に電流源からの1/f 雑音がリング発振器でアップコンバージョンされることによる位相雑音の劣化が一番大きな原因の一つである。

本研究では、リング発振器の低雑音電流源について考察する。また、ローパスフィルタを用いて電流源の 1/f 雑音がアップコンバージョンされるのを防ぐ回路を提案し、シミュレーションにより検証する。

## 2 回路構成

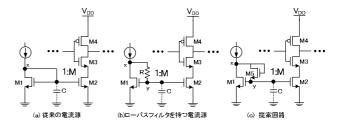

図1に電流源を持つリング発振器の回路図を示す。図1(a)は従来の電流源を持つインバーター型のリング発振器である。電流源(M1)の1/f 雑音が発振周波数へアップコンバージョンされるのを防ぐために、12nFという大きいキャパシタを外付けで用いる方式が紹介されている[1],[2]。

図 1(b)に示すように、ローパスフィルタを持つ電流源を提案する。 ノード x から y への伝達関数は RC 直列のローパスフィルタに相当する。一方、電流源の 1/f 雑音をカットするためには非常に大きい RC の値が必要である。例えば、C=10pF の場合、R は  $1M\Omega$ 以上のものが望ましい。

図 1(c)はローパスフィルタを持つ電流源の提案回路である。R の代わりに NMOS のダイオード接続を用いて、高い抵抗を実現したものである。このダイオード接続にはほとんど電流が流れないため、等価的に 1MΩ以上の抵抗として利用できる。よって、ローパスフィルタを持つ電流源が小面積で構築できる。

### 3 シミュレーション結果

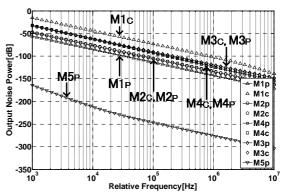

図 2 は、3 段のリング発振器において、各 MOS の 1/f 雑音の出力雑音電力への寄与度を比較したものである。小文字 c は従来方式(図 1(a))で、p は提案方式(図 1(c))を意味する。電流源(M1)の出力雑音が 40dB 程度低減するのを確認した。表 1 にリング発振器のシミュレーション結果を示す。消費電力の増加なしに、位相雑音が 10dB 程度低減するのを確認した。

#### 4 **まとめ**

リング発振器用のローパスフィルタを持つ電流源を提案した。電流源(M1)の 1/f 雑音が発振周波数へアップコンバージョンされるのを抑制することにより、同一リング発振器において位相雑音が 10dB 程度低減できることをシミュレーションで確認した。

図1 電流源を持つリング発振器

図 2 MOS の 1/f 雑音の出力雑音電力への寄与度の比較

表 1. シミュレーション結果比較

|                     | The Proposed | The conventional |

|---------------------|--------------|------------------|

| Process             | CMOS 0.18µm  | CMOS 0.18µm      |

| Supply (V)          | 1.8          | 1.8              |

| Frequency (GHz)     | 1.55         | 1.54             |

| PN@10 kHz (dBc/Hz)  | -49.6        | -39.1            |

| PN@100 kHz (dBc/Hz) | -78.3        | -67.4            |

| PN@600 kHz (dBc/Hz) | -98.2        | -88.2            |

| PN@1 MHz (dBc/Hz)   | -103.3       | -93.9            |

| Current (mA)        | 2.58         | 2.58             |

#### 謝辞

本研究の一部は、総務省委託研究『電波資源拡大のための研究開発』、 半導体理工学研究センター、NEDO、並びに東京大学大規模集積システム設 計教育研究センターを通し、日本ケイデンス株式会社およびアジレント・ テクノロジー株式会社の協力で行われたものである。

#### 参考文献

- [1] L. Dai and R. Harjani, "Analysis and design of low-phasenoise ring oscillators," in *Proc. IEEE Int. Symp. Low Power Electronics and Design (ISLPED)*, Rapallo, Italy, 2000, pp. 289–294.

- [2] Asad A. Abidi, "Phase Noise and Jitter in CMOS Ring Oscillators," *IEEE J. Solid-State Circuits*, vol. 41, no. 8, pp. 1803–1816, Aug. 2006