# Thermal Noise Effects Caused by Settling Time Optimization in Switched-Capacitor Circuits

ドン ター ゴク ヒュイ,宮原 正也,松澤 昭 東京工業大学大学院理工学研究科 電子物理工学専攻

#### 発表内容

- ■背景·目的

- ■ポール・ゼロキャンセル法

- ■ノイズへの影響

- まとめ

#### 発表内容

- ■背景·目的

- ■ポール・ゼロキャンセル法

- ■ノイズへの影響

- まとめ

TOKYO TECH

#### 背景・目的

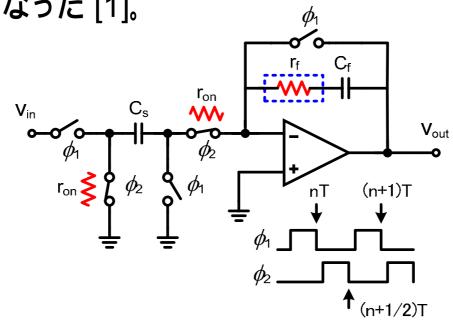

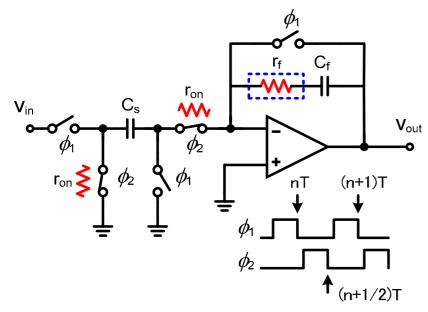

■ ポール・ゼロキャンセル法でセットリング時間を大幅に改善できることが明らかになった [1]。

Charge-redistribution SC amplifier with an added resistance

- ポール・ゼロキャンセル法を用いた際、ノイズを検討。

- ポール・ゼロキャンセル法の電力効率を評価。

[1] M. Miyahara and A. Matsuzawa, IEICE Trans. Electron., vol. E90-C, no. 6, pp. 1165-1171, June 2007.

Pursuing Excellence

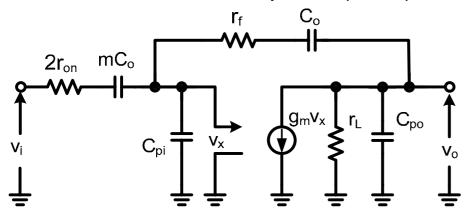

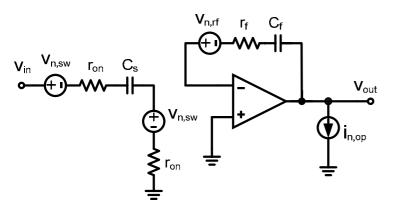

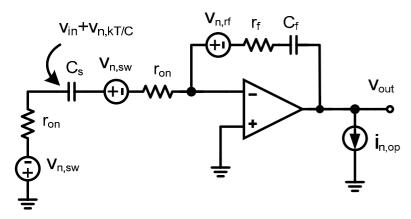

#### 解析モデル

解析を行う SC Amplifier (SCA)

SCAのホールドフェーズの小信号等価回路

#### 以下を仮定

- 出力抵抗は十分に大きい、g<sub>m</sub>r<sub>L</sub>>>1

- C<sub>pi</sub>はC<sub>0</sub>と比較して十分小さい

- オペアンプは位相補償されているTable 1 Model parameters

| r <sub>on</sub> | <b>g</b> m | m | <b>C</b> <sub>pi</sub> | C <sub>po</sub> | C <sub>0</sub> |

|-----------------|------------|---|------------------------|-----------------|----------------|

| 50 Ω            | 1 mS       | 1 | 100 fF                 | 300 fF          | 6 pF           |

**r**on: スイッチオン抵抗

**C**<sub>pi</sub>, **C**<sub>po</sub> : オペアンプ入出力寄生容量

$g_{\rm m}$ :トランスコンダクタンス

rL:オペアンプ出力抵抗

$C_0$ : 单位容量

- ■背景·目的

- ■ポール・ゼロキャンセル法

- ■ノイズへの影響

- まとめ

## ポール・ゼロキャンセル法

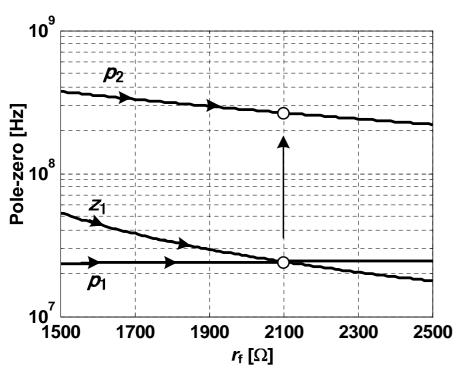

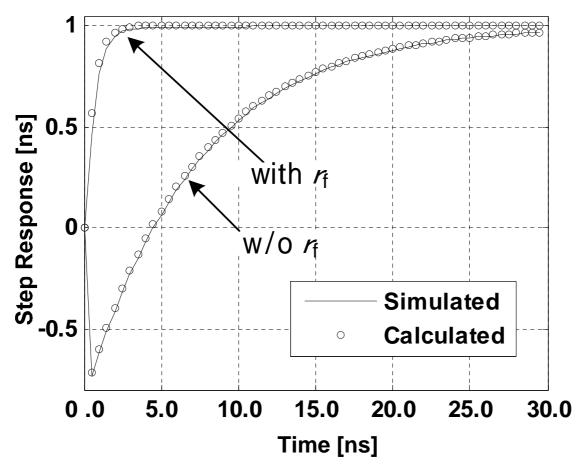

■ 第1ポールとゼロがキャンセルし、主要極が第2ポールにシフトする。

Pole-zero vs. switch resistance  $r_{\rm f}$

▶ ポール・ゼロキャンセル条件:

$$r_{\rm f \ opt} = 2mr_{\rm on} + \frac{m+1}{g_{\rm m}}$$

$$v_{\text{out}} = -\frac{s + z_1}{(s + p_1)(s + p_2)}v_{\text{in}}$$

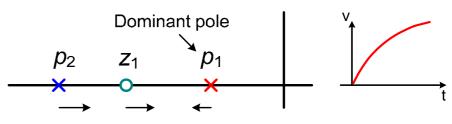

(a) セットリング時間の改善前

(b) セットリング時間の改善後

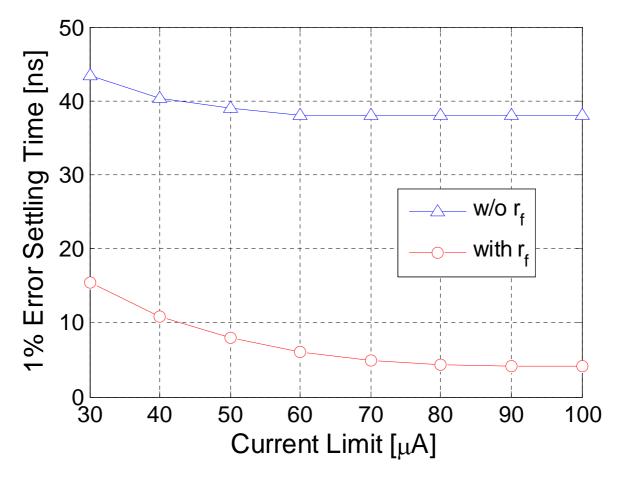

#### セットリング時間の改善

TOKYO TECH

■ ポール・ゼロキャンセル法により、1%エラーのセットリング時間が 38.0nsから4.1nsに改善

Step response of the close-loop system

& Okada Lab.

Dong, Tokyo Tech.

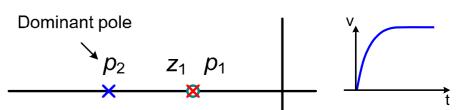

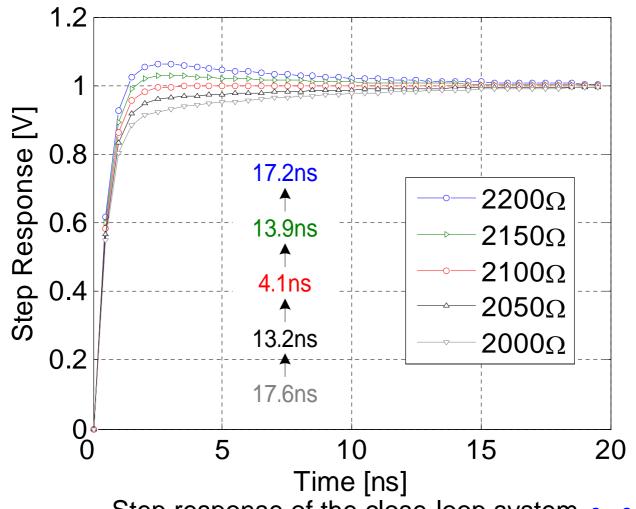

#### r<sub>f</sub>値が最適値からずれた場合

*TOKYOTECH* マメベ `ヌ⇔≐Ω

■ r<sub>f</sub>が最適値からずれると、セットリング時間が長くなるが、通常設計よりは短い(通常設計の1%エラーセットリング時間は38.0ns)。

Step response of the close-loop system

Dong, Tokyo Tech.

Matsuzawa & Okada Lab.

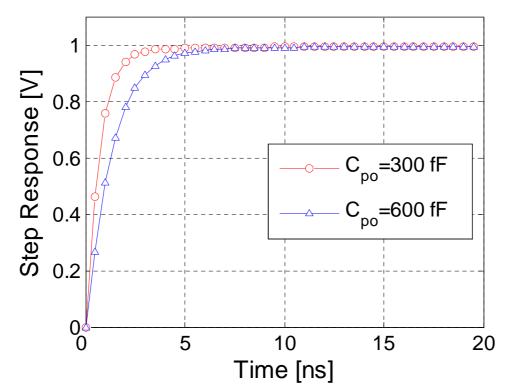

#### セットリング時間の調整

■ セットリング時間の短縮 = 主要極を大きくする

$$p_{\text{dom}} = \frac{g_{\text{m}}}{(m+1)C_{\text{po}}}$$

- ✓ g<sub>m</sub>を大きく

- ✓ mを小さく

- ✓ 出力寄生容量Cpoを小さく

▶ 更に、過度な高速化が不要な場合はC<sub>po</sub>することで、セットリング時間を簡単に 調整できる。

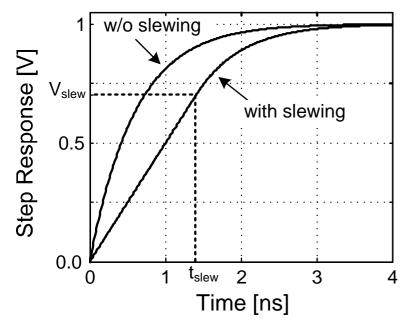

#### スルーイング

セットリングが速いシステムはスルーイングを受けやすい。

$$g_{\rm m} pprox rac{2I_{

m bias}}{V_{

m eff}}$$

: トランスコンダクタンス

$$SR = \frac{I_{\text{bias}}}{C_{\text{off}}} : \lambda J V - V - F$$

$$C_{\text{eff}} \approx C_{\text{L}} + \frac{C_{\text{s}}C_{\text{f}}}{C_{\text{c}} + C_{\text{s}}}$$

: 実効負荷容量

$$V_{\text{out}}(t) = V_{\text{in}} \cdot \left(1 - e^{-t/\tau}\right)$$

スルーイングが起こる条件:

$$\frac{d}{dt}V_{\text{out}}(t)\Big|_{\text{max}} = \frac{V_{\text{in}}}{\tau} > SR$$

スルーイングが起こった時:

$$t \le t_{\text{slew}} \quad V_{\text{out}}(t) = SR \cdot t$$

$$t > t_{\text{slew}} \quad V_{\text{out}}(t) = SR \cdot t_{\text{slew}} + (V_{in} - SR \cdot t_{\text{slew}})$$

$$\times \left(1 - e^{-\frac{t - t_{\text{slew}}}{\tau}}\right)$$

ただし、 $t_{

m slew} = rac{V_{

m in}}{SR} - au$

Mat & C

#### スルーイングとセットリング時間

TOKYO TECH-

スルーイングが起こった時、セットリング時間が長くなる。

スルーイングを含むセットリング時間

- ■背景·目的

- ■ポール・ゼロキャンセル法

- ■ノイズへの影響

- まとめ

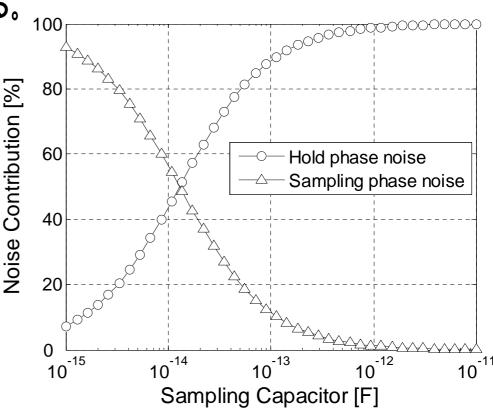

## 2-フェーズシステムのノイズ

■ ポール・ゼロキャンセル法を用いた場合、Csを大きくするどボール ドフェーズノイズが支配的になる。

Equivalent circuit in sampling phase

Equivalent circuit in hold phase

Relative contributions from sampling phase noise and hold phase noise to the total noise

TOKYO TECH

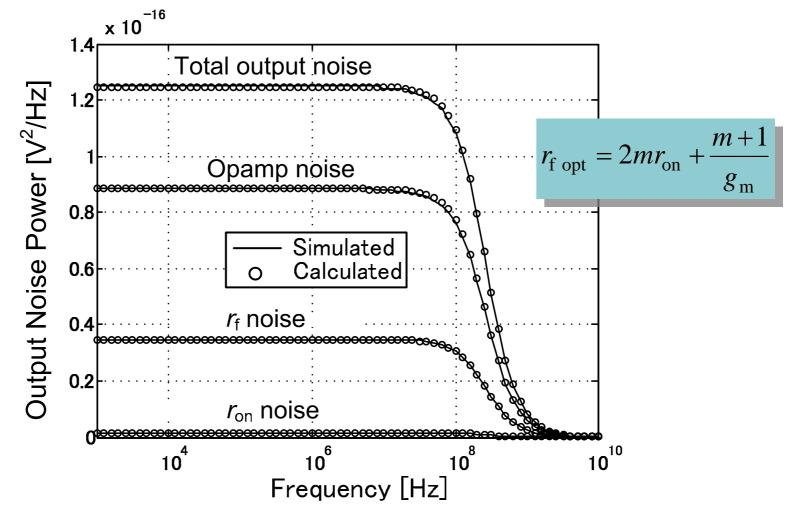

#### ホールドフェーズノイズ

■ ローパワー設計(gmが小さい)では、オペアンプノイズが支配的

になる。

Noise sources in hold phase

Dong, Tokyo Tech.

& Okada Lab.

#### オペアンプノイズの広帯域化

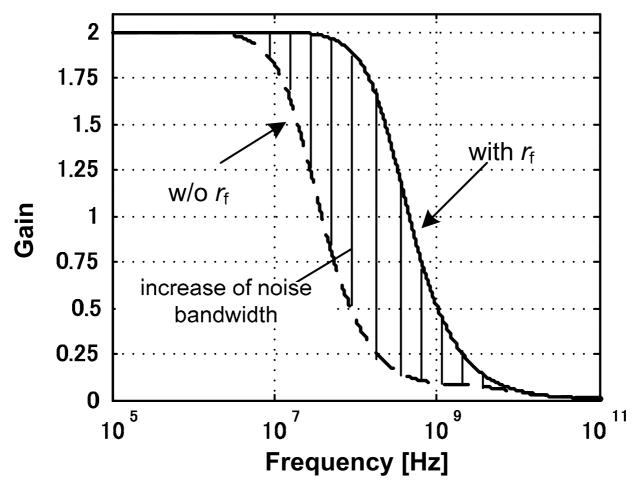

■ ポール・ゼロキャンセル法を用いた場合、オペアンプノイズの帯域が広がる。

Frequency response of the opamp noise transfer function

Dong, Tokyo Tech.

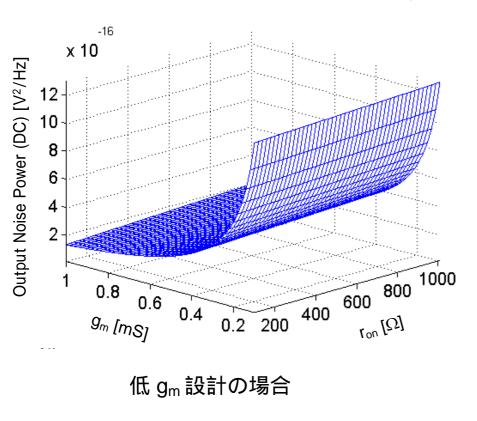

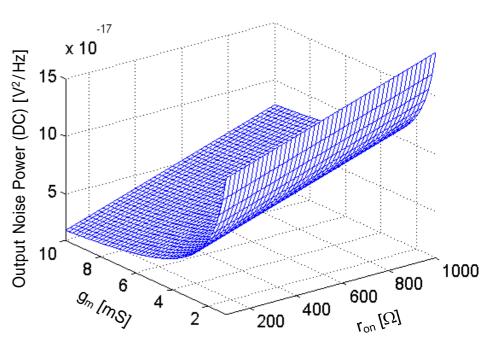

#### スイッチオン抵抗ノイズ

■ 低電力 (低g<sub>m</sub>)設計では、スイッチオン抵抗のノイズの影響が小さい。

■ 高速 (高 g<sub>m</sub> )設計では、スイッチオン抵抗のノイズの影響が大きい。

高 gm 設計の場合

▶ スイッチオン抵抗を最適設計する必要がある。

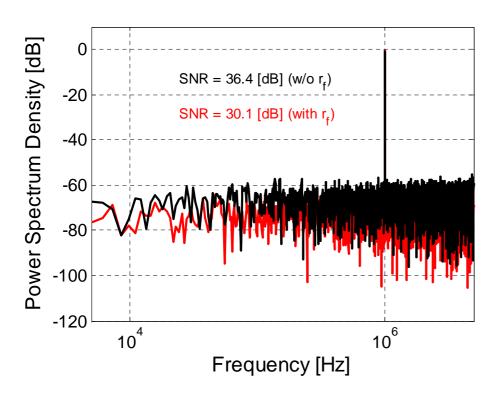

#### SNR劣化と電力効率

全体ノイズが増加するため、SNRは6.3dB劣化

電力効率(Figure-of-Merit)

$$\mathsf{FoM} = \frac{P}{f_{\mathsf{B}} \times \mathsf{SNR}}$$

ただし、fa:信号帯域、P:は消費電力

- ポール・ゼロキャンセル法では、

- 信号帯域が9.3倍改善

- SNRが6.3dB (4.3倍)劣化

- ▶ FoMは約1/2改善

SCA output spectrum with 400mVpp sine input

プラー・プロキャンセル法は電力効率が良い。

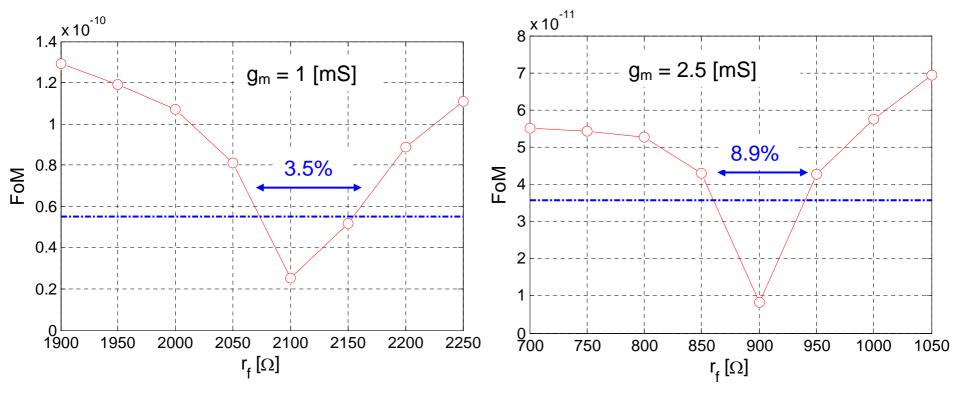

#### r<sub>f</sub>が最適値からずれると、電力効率が低下

- 問題点:rfの要求精度が高い

- > 今後課題:m, r<sub>on</sub>, g<sub>m</sub>の最適設計

$$r_{\rm f \ opt} = 2mr_{\rm on} + \frac{m+1}{g_{\rm m}}$$

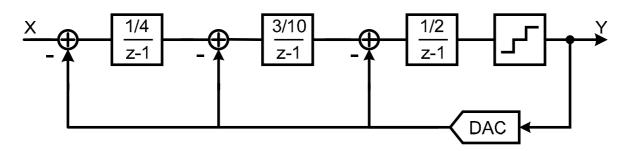

#### 応用例:ΣΔADC

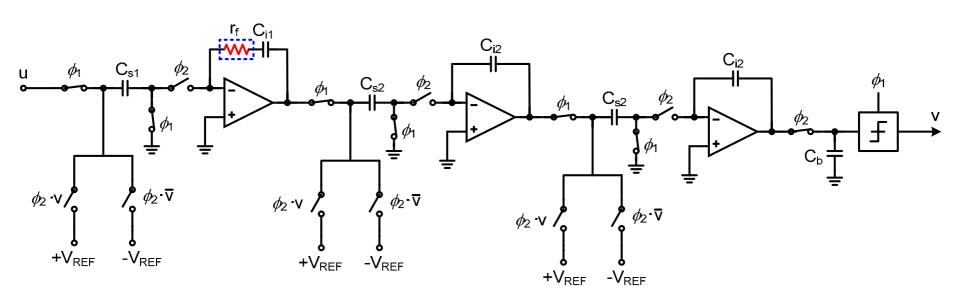

Single-loop third-order topology

Schematic of the proposed topology

**Pursuing Excellence**

ΤΟΚΥ

#### シミュレーション結果

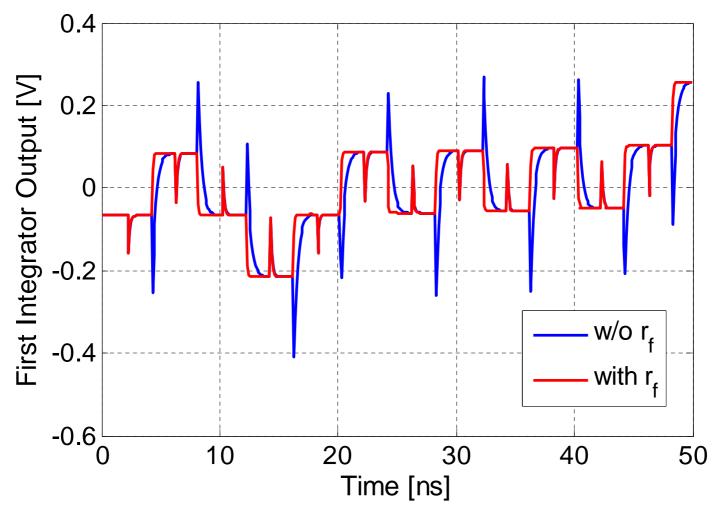

■ ポール・ゼロキャンセルを用いた方が応答が速い

Transient Simulation Result

Dong, Tokyo Tech.

**Pursuing Excellence**

#### ジッタを含むシミュレーション結果

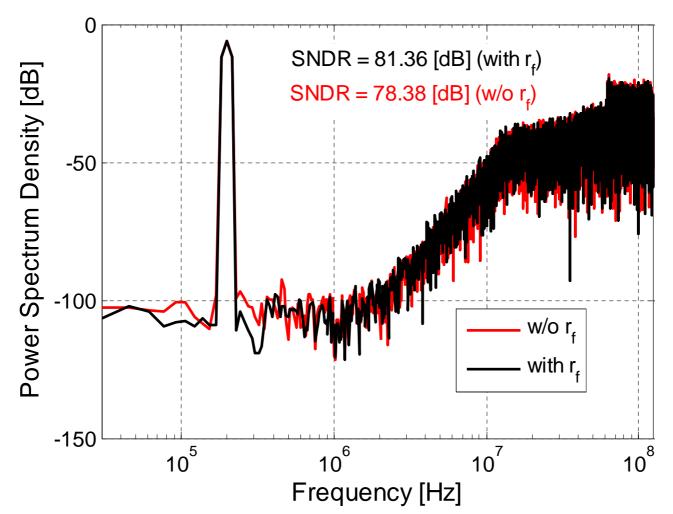

■ ポール・ゼロキャンセル法で、SNDRが3dB改善

-6dBFS input, 1% Jitter ( = 40p) Simulation Result

- ■背景·目的

- ■ポール・ゼロキャンセル法

- ■ノイズへの影響

- まとめ

- ポール・ゼロキャンセル法で、スイッチトキャパシタ回路 のセットリング時間が大幅に改善できる。

- この方法では、ノイズの広帯域化と、挿入したフィード バック抵抗のノイズにより、全体ノイズが増加することを 示した。

- ただし、電力効率の面から、ポール・ゼロキャンセル法 が有効であることが明らかになった。