## A-D変換器の新たな地平拓く 極限に迫る低消費技術が登場

松澤昭 東京工業大学

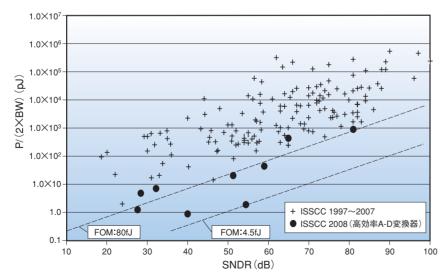

ISSCC 2008 におけるデーター・コンバータ(A-D変換器/D-A変換器)分野の注目は、A-D変換器のエネルギ効率の向上が一気に進んだことである。すなわち、変換速度や変換精度といった性能当たりの消費電力を大幅に低減した(図10)。特に逐次比較(SAR)型A-D変換器のエネルギ効率向上が著しい。

その中でも最も注目すべき論文は、1 変換ステップ当たりの消費エネルギ量を表す FOM (Figure of Merit) \* <sup>1)</sup>が 4.4 fJと極めて低い逐次比較型 A-D 変換器だろう。オランダ University of Twenteとオランダ Philips Research 社が共同で開発した (講演番号 12.4) <sup>† 9)</sup>。この 4.4fJという FOM は驚異的だ。極限値

といってよいほど低い。A-D変換器の新たな地平を拓 く成果だといえよう。

FOMの急激な低下は、 ここ数年間にわたる傾向で ある。例えば、現在最も活

発に開発されている高速 A-D 変換器の ISSCC 2006における FOMは 500fJ 程度だった。これが ISSCC 2007には一気に 1/10近くの 65fJ まで低下した。これは、ベルギー IMEC が発表した逐次比較型 A-D 変換器の値である。帰還用の内部 D-A 変換器に電荷再分配方式を採用することなどで達成した†100。この成果にも十分驚いたが、今回はそれよりもさらに 1/10以上も低い 4.4fJ である。まさに世界中の研究者が卒倒するほどの低い値をたたき出した。

逐次比較型 A-D 変換器は、原理的には「究極の低消費電力化」を実現できる可能性を秘めたアーキテクチャである。オペアンプなど、アナログ回路に通常は欠

かせない、定常的に電流を消費する回路 要素を使わずに構成できるからだ。具体 的には、静電容量(コンデンサ)とスイ ッチ、比較器のほかは、デジタル回路だ けで構成可能である。そうはいっても、 数 fJ と低い FOM がこれほどすぐに達成 されるとは思ってもいなかった。

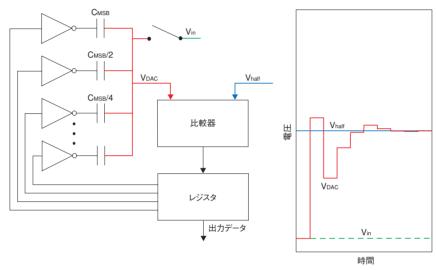

今回University of Twenteらがこの FOM を達成できたポイントはいくつかある。最初に挙げられるのは、図11に示した通り、回路構成が極めて簡素なことだろう。つまり、2 進数を係数に使って重み付けしたコンデンサを並べたコンデンサ・アレイを用意して、各コンデンサを論理インバータで駆動するだけで、電荷再分配方式の内部 D-A 変換器を実現している。こうした簡素な回路構成ながらも、A-D変換器としては10ビットの分解能と1Mサンプル/秒の変換速度を確保し、消費電力を1.9 μ W に抑えた。この技術力はかなり高いと評価できる。

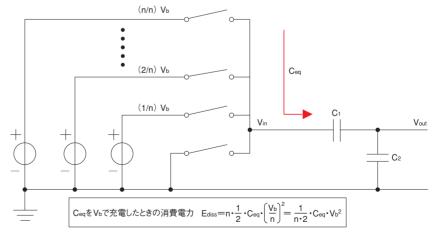

そしてこのA-D変換器で最も面白いポイントは、逐次比較型A-D変換器の原理的な特徴である低い消費電力に駄目を押す格好で、消費電力をさらに低減する「断熱充電技術」を適用したことである。この技術はデジタル回路に向けた低消費

図 10 A-D変換器のエネルギ効率がいっそう高まる

1997~2007年のISSCCで発表されたA-D変換器と、ISSCC 2008で発表されたA-D変換器について、変換精度とエネルギ効率を比較した。横軸には変換精度の指標である SNDR (Signal to Noise and Distortion Ratio) をプロットした。縦軸にはエネルギ効率の指標として、消費電力 (P) を帯域幅 (BW) の2倍の値で割って求めた、変換速度当たりの消費電力をpJ (ピコジュール) の単位でプロットした。出典:ISSCC

\*1) A-D変換器のFOM(Figure of Merit)は次式で求められる。ただしPは消費電力、2×BWeff, Fs は実効帯域幅(BWeff)を2倍した値もしくはサンプリング周波数(Fs)のいずれか一方、ENOBは有効ビット分解能、ECONVERSIONは変換ステップ当たりの消費エネルギである。

$$FOM \!=\! \frac{P}{(2 \!\times\! BW_{\text{eff}},F_S) \!\times\! 2^{ENOB}} = \! \frac{E_{CONVERSION}}{2^{ENOB}}$$

### 参考文献

- <sup>f 9)</sup>M. van Elzakker, E. van Tuijl, P. Geraedts, D. Schinkel, E. Klumperink, B. Nauta, "A 1.9 µ W 4.4fJ/conversionstep 10b 1MS/s Charge-Redistribution ADC," ISSCC 2008, Feb. 2008.

- <sup>† 10)</sup>松澤昭、「A-D変換器の注目論文を解説、各 方式とも着実に進化」、*EE Times Japan*、 2007年4月号 (no.22)、pp.47~49.

www.eetimes.jp 2008.03 EE Times Japan

# Cover Story

電力化技術としては知られていたが、これまでアナログ回路にはほとんど用いられていなかった。

断熱充電とは、コンデンサを充電する際に高い充電電圧をいきなり印加するのではなく、低い電圧から時間をかけてじわじわと充電電圧を高める技術である。こうすれば、充電電圧を供給する電源とコンデンサの電極電圧との間の電位差を常に低く抑えられる。従って、電源とコンデンサの間に挿入されたスイッチの抵抗成分による電力消費(ジュール熱損失)を低減できる仕組みだ。理論的には、充電電圧を高める過程を n 回のステップに分けることで、ジュール熱損失を 1/nに低減できる(図12)。

実際には、内部 D-A 変換器のコンデンサ・アレイを充放電する処理にこの断熱充電技術を適用した。充電電圧を高めるステップ数は3に設定している。ステップ数が多ければ多いほど前述の通りジュール熱損失を低く抑えられるが、制御用のデジタル回路の規模が大きくなってその消費電力が増えるというトレード・オフが発生するからだ。

## 逐次比較型の実用性が高まる

このほかにもISSCC 2008では、逐次比較型A-D変換器による高エネルギ効率変換技術の発表が相次いだ。その中でも、記録的な性能の達成という際立った成果は上げていないものの、実用性の点で優れていたのが、9ビットの分解能で40Mサンプル/秒の変換速度を820μWの消費電力で達成した逐次比較型A-D変換器だろう。IMECとイタリアのUniversity of Salentoが共同で開発した(講演番号12.1)†11)。

画像処理や無線通信のベースバンド信号処理などの用途では、10ビット程度の分解能と50Mサンプル/秒程度の変換速度が必要になる。ところがこれまでに

52

開発されてきた逐次比較型 A-D 変換器は、6 ビット、数 M サンプル/秒にとどまるものが多かった。これでは用途がかなり限定されてしまう。今回のIMECらの成果は、逐次比較型 A-D 変換器の用途

#### 参考文献

† 110 V. Giannini, P. Nuzzo, V. Chironi, A. Baschirotto, G. Van der Plas, J. Craninckx, "An 820 μW 9b 40MS/s Noise-Tolerant Dynamic-SAR ADC in 90nm Digital CMOS," ISSCC 2008, Feb. 2008.

### 図 11 電荷再分配方式の逐次比較を簡単に実現

$C_{MSB}$ 、 $C_{MSB}/2$ 、 $C_{MSB}/4$  …と2進数で重み付けしたコンデンサ・アレイを論理インバータで駆動する簡単な回路で、電荷再分配方式の内部 D-A 変換器を構成した。この出力電圧( $V_{DAC}$ )と参照電圧( $V_{half}$ )の大小を比較器で比べることで、最上位ビット(MSB)から順番に、A-D 変換器の出力データを逐次決定する。

### 図 12 断熱充電回路の動作

$C_1 \geq C_2$ を直列に接続した際の等価的な静電容量( $C_{eq}$ )を $V_b$ で充電する場合の模式図である。充電電圧をn回のステップに分割して段階的に高めていく。まず(1/n) $V_b$ 、次に(2/n) $V_b$ と、順番にスイッチをオンに切り替える。最後に (n/n)  $V_b$ のスイッチをオンすれば、最終的な充電電圧である $V_b$ が印加される仕組みだ。こうすれば、スイッチの抵抗成分による無駄な電力消費( $E_{diss}$ )を 1/n 倍に減らせる。実際にはこれを電荷再分配方式の内部 D-A 変換器に適用した。

EE Times Japan 2008.03 www.eetimes.jp

を広げるものだといえる。

逐次比較型 A-D 変換器では前述の通り オペアンプを使わない。このため、分解 能を高めるには比較器の感度を高めるこ とが不可欠である。すなわち比較器にお いて熱雑音の影響を低く抑えることが必 要だ。ただし感度の改善は、理論的には 応答速度の低下や消費電力の増大を招い てしまう。そこで IMEC らは今回、この 課題を回路技術によって解決した。

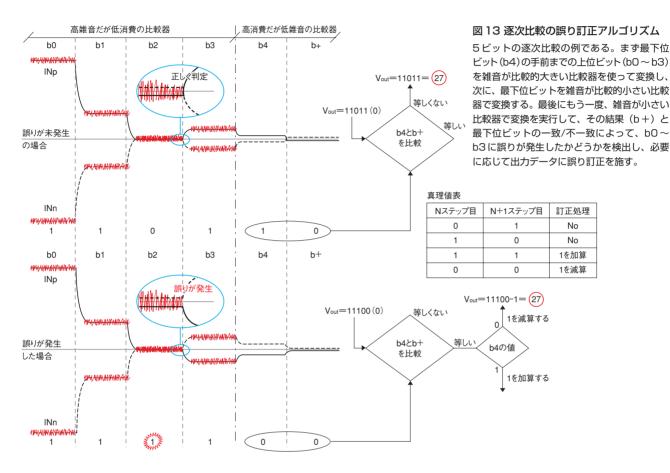

具体的には、感度は低い(雑音が大きい)が消費電力が低い比較器と、感度は高い(雑音が小さい)が消費電力が高い比較器を用意して、どちらか一方のみを逐次変換アルゴリズムに従って動作させることで、消費電力の増大を抑えつつ、比較器の感度に起因した誤りが発生しないようにした。

## アルゴリズム工夫し誤り訂正

採用した逐次変換アルゴリズムはこうだ(図13)。Nビットの変換処理において、まず、最上位ビットの変換処理(1ステップ目)から最下位ビットの1つ手前のビットの変換処理(N-1ステップ目)までは低感度・低消費電力の比較器を使って実行する。この期間は、比較器の雑音が大きいため各ビットを誤って判定する危険性がある。ただし比較器の実効的な雑音電圧は最下位ビット(LSB)に相当する電圧振幅の1/2以下に抑えてあるため、A-D変換後のデジタル・データ(2進数)に発生する誤りの大きさは最大でも1である。

そこで、最下位ビットの比較処理(N ステップ目)は高感度・高消費電力の比較器に切り替えて、誤った判定を防ぐ。 さらに、低感度の比較器を使った以前の ステップで誤りが発生していたかどうか を検出し、誤りが発生していた場合はそ れを訂正する処理を実行する。

誤りの検出は簡単だ。同じく高感度の比較器を使って追加の変換処理(N+1ステップ目)を実行し、Nステップ目の結果と比較すればよい。もし誤りが発生していれば両者が一致するため、LSBが0だったら1を引き、LSBが1だったら1を足して誤りを訂正する。誤りが発生していなければ両者は一致せず、その場合は訂正処理を実行する必要はない。

90nmのCMOS技術で製造した。 FOMは54fJと非常に小さい。この成果が示すように、逐次比較型A-D変換器の開発は今後、これまでのようにさらなる低消費電力化を追求する動きよりも、

53

www.eetimes.jp 2008.03 EE Times Japan

# Cover Story

FOMをこれまでのレベルに維持したまま、10ビット以上の高精度化や50Mサンプル/秒以上の高速化を目指す動きが強まるものと思われる。

## 160個並列で24GS/s達成

変換エネルギ効率が高いという逐次比較型 A-D 変換器の特徴を生かした応用の1つに超高速 A-D 変換器がある。すなわち、数多くの逐次比較型 A-D 変換器コアを用意して並列に接続し、時間的にインターリーブ動作させることで高い変換速度を実現する。

こうしたコンセプトは従来から提案されており、それ自体に目新しさはない。しかしISSCC 2008ではこのコンセプトの可能性を徹底的に追求し、6ビットの分解能で24Gサンプル/秒と極めて高い変換速度を達成したA-D変換器が登場し、聴講者の関心を集めていた。

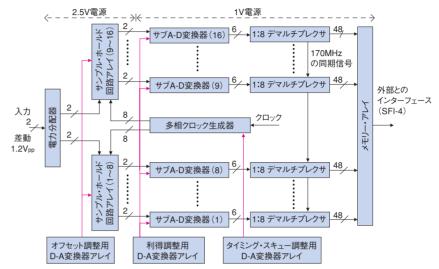

カナダNortel 社と伊仏合弁STMicroelectronics 社が共同で開発した(講演番号30.3) † 12)。回路構成は**図14**に示す通りである。16個のサブA-D変換器を備えており、そのサブA-D変換器それぞれが、さらに10個の逐次比較型A-D変換器(単位A-D変換器)から構成されている。すなわち全体では160個の単位A-D変換器がインターリーブ動作するわけだ。従って、各単位A-D変換器は150MHzで動作するとみられる。

このアーキテクチャでは、数多くの A-D 変換器を用いるため、互いの特性のばらつきが問題になりやすい。そこで、サブ A-D 変換器でとのオフセットや利得、タイミング・スキューのばらつきを補正する機能を備えた。

5ビットのENOB(有効ビット分解能)が得られる帯域幅としては6GHz程度を確保している。90nmのCMOS技術で製造した。消費電力は1.2W、専有面積は16mm<sup>2</sup>である。24Gサンプル/

54

図 14 24Gサンプル/秒の6ビットA-D変換器

回路ブロック図である。16個のサブA-D変換器を並列に接続し、インターリーブ動作させることで24Gサンブル/秒と極めて高い変換速度を実現した。各サブA-D変換器は10個の単位A-D変換器からなる。サブA-D変換器ごとの特性のばらつきを補正するために、オフセットと利得、タイミング・スキューそれぞれをデジタル制御で調整するD-A変換器アレイを設けた。

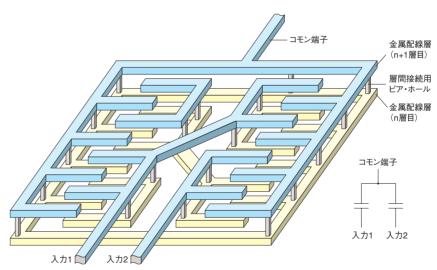

図 15 インターリーブ型コンデンサ

多層配線を使って形成したコンデンサである。くしの歯状の配線を上下それぞれの配線層に設けてビア・ホールで接続したものをコンデンサの一方の電極とし、2つの電極をくしの歯をかみ合わせるように重ねることでコンデンサとして機能させる「インターリーブ型」だ。

秒という変換速度は目を見張る性能だが、消費電力と専有面積については、際立った成果というわけではない。

例えば、2007年にルネサス テクノ ロジが発表した並列型の6ビット・フラッ

### 参考文献

† 12) P. Schvan, J. Bach, C. Falt, P. Flemke, R. Gibbins, Y. Greshishchev, N. Ben-Hamida, D. Pollex, J. Sitch, S-C. Wang, J. Wolczanski, "A 24GS/s 6b ADC in 90nm CMOS," ISSCC 2008, Feb. 2008.

EE Times Japan 2008.03 www.eetimes.jp

シュ型 A-D 変換器<sup>† 13)</sup>と比較してみよう。 ルネサスのこの開発品も、同じく90 nmのCMOS技術で製造されており、変 換速度は3.5G サンプル/秒、消費電力 は98mW、専有面積は約0.15mm<sup>2</sup>で ある。

ここで、Nortel社らの今回の開発品とルネサスの開発品それぞれの消費電力と専有面積を1Gサンプル/秒当たりの値に換算すると、消費電力は今回が50mW、ルネサルスが28mWで、専有面積は今回が0.667mm²、ルネサスが0.043mm²であり、いずれもルネサスの開発品の方が優れている。

この比較結果から分かる通り、確かに 逐次比較型 A-D 変換器は変換エネルギ を低く抑えられるが、変換速度そのもの は高くないので、並列化によるインター リーブ動作を使って変換速度を高める と、専有面積が大きくなったり、さまざ まな調整回路が必要になったりするため、 設計上のオーバーヘッドが生じやすい。 従って今後の開発においては、どういっ た変換方式をどのように組み合わせる手 法が最も妥当かという検討が盛んになる ものと思われる。

## パイプラインも負けていない

エネルギ効率が高いA-D変換器といえば、最近は逐次比較型ばかりが注目されているが、パイプライン型も決して負けてはいない。ISSCC 2008では、10ビットの分解能で100Mサンプル/秒の変換速度を備えながらも、消費電力が4.5mWと非常に低いパイプライン型A-D変換器をSTMicroelectronics社が発表した(講演番号12.7)†14)。FOMは62fJで、逐次比較型にも引けを取らないような高いエネルギ効率を達成した。65nmのCMOS技術で製造しており、専有面積は380μm×180μm(約0.07mm²)と極めて小さい。

回路構成そのものは標準的なパイプライン型だが、コンデンサやトランジスタなどの素子(デバイス)形成方法を低電圧動作のアナログ回路に向けて改良したようだ。例えばコンデンサについては、従来のMIM(Metal Insulator Metal)コンデンサを使う代わりに、図15に示すように多層配線を用いて形成している。単位面積当たりの静電容量が2fF/μm²と一般的なMIMコンデンサに比べて2倍程度も高い上に、静電容量の精度も高い(静電容量のばらつきが少ない)。従って、小さな面積で高精度のA-D変換器を実現できる。

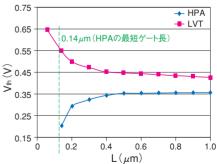

トランジスタについては、通常はショートチャネル効果を抑える目的で施すポケット・イオン注入を使わない、アナログ回路専用のトランジスタを開発したようだ。スイッチとして動作させる際に、図16に示すようにオン抵抗を低く、ドレイン抵抗を高くできるので、低い電源電圧で動作する高性能のアナログ回路に

適している。

このほか発表論文では言及されていないが、この手法を使うと理論的にはしきい値電圧(Vth)のばらつきも小さくできるはずである。このように、デバイス開発によって性能を高めるというアプローチも重要である。

このSTMicroelectronics社の成果のように、FOMが低いA-D変換器をパイプライン型でも実現できるとなれば、「最適なアーキテクチャは何か」という論争が今後しばらく続くことになりそうである。

#### 参考文献

- <sup>† 13)</sup>K. Deguchi, N. Suwa, M. Ito, T. Kumamoto, T. Miki, "A 6-bit 3.5GS/s 0.9V 98mW Flash ADC in 90nm CMOS," 2007 Symposium on VLSI Circuits, Jun. 2007.

- <sup>† 14)</sup>M. Boulemnakher, E. Andre, J. Roux, F. Paillardet, "A 1.2V 4.5mW 10b 100MS/s Pipelined ADC in 65nm CMOS," ISSCC 2008, Feb. 2008.

### (a) 相補型スイッチ回路

(b) Vin対Ron特性

## (c)L対Vth特性

55

図 16 低電圧アナログ向けにトランジスタ改良

低電圧動作のアナログ回路に向けてトランジスタの特性を改良したプロセス(HPA)と、標準的な低しきい値電圧トランジスタに対応したプロセス(LVT)それぞれを使って、 $nMOS \ge pMOS$  をパス・トランジスタとして組み合わせた相補型スイッチ回路(a)を構成し、特性を比較した。入力電圧 ( $V_{in}$ ) に対するオン抵抗 ( $R_{on}$ ) の特性 (D) と、ゲート長 (D) に対するしきい値電圧 (D) の特性 (D) を示している。

www.eetimes.jp 2008.03 EE Times Japan