## スイッチのオン抵抗が パイプライン型ADC性能に及ぼす影響と セトリング時間最適設計技術の検討

〇宮原 正也、松澤 昭 東京工業大学大学院 理工学研究科電子物理工学専攻

## 発表内容

- 1. 背景•目的

- 2. SWのON抵抗がMDACの性能へ与える影響

- ●解析モデル・応答式の導出

- ●スイッチON抵抗のセトリングへの影響

- ●スイッチON抵抗の最適化

- ●ポール・ゼロ解析

- 3. マルチビットMDACの性能解析

- ●小信号解析(Slewingを含まない場合)

- ●大信号解析(Slewingを含む場合)

- 4. まとめ

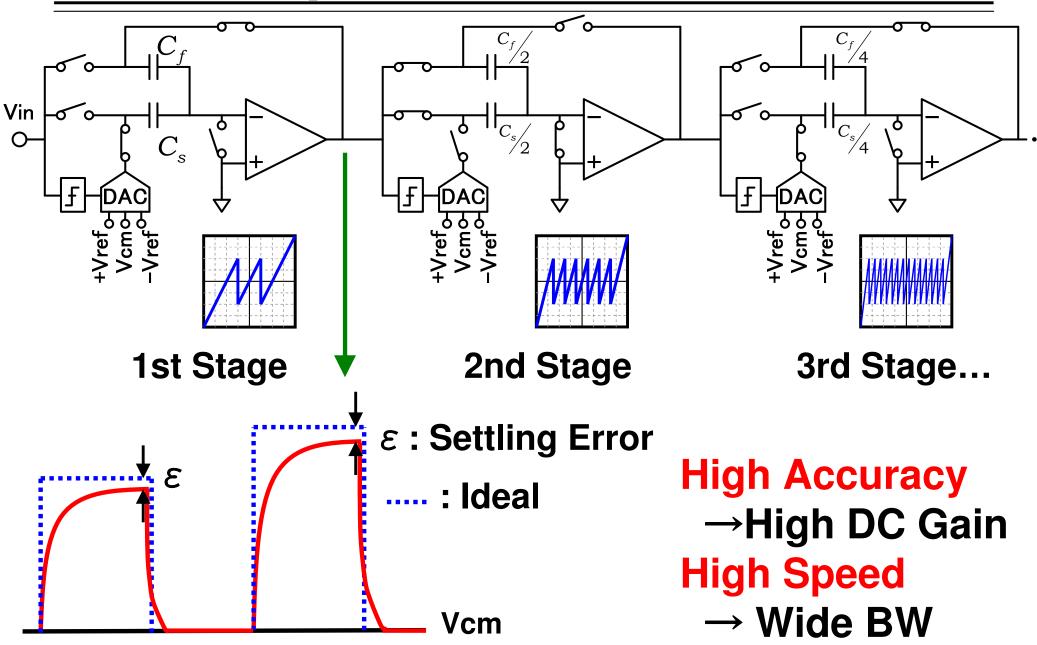

## 1. Pipelined ADC (1.5bit)

### 2. 背景 目的

- 1. SWのON抵抗がMDACの性能に与える影響を明らかにする。

- 2. セトリング時間を最短にするSWのON抵抗条件を導出する。

- 3. SWの最適化を生かすMDACの構成について考える。

## 発表内容

- 1. 背景•目的

- 2. SWのON抵抗がMDACの性能へ与える影響

- ●解析モデル・応答式の導出

- ●スイッチON抵抗のセトリングへの影響

- ●スイッチON抵抗の最適化

- ●ポール・ゼロ解析

- 3. マルチビットMDACの性能解析

- ●小信号解析(Slewingを含まない場合)

- ●大信号解析(Slewingを含む場合)

- 4. まとめ

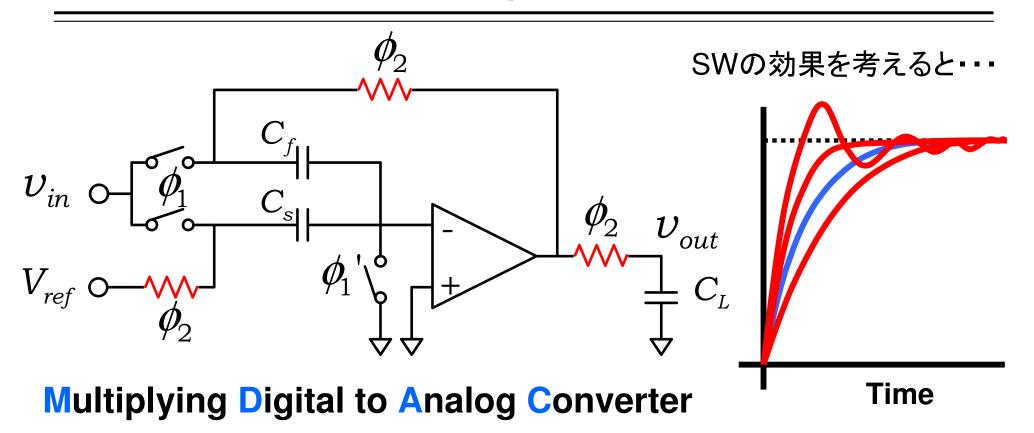

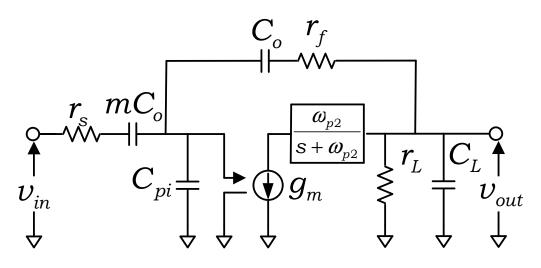

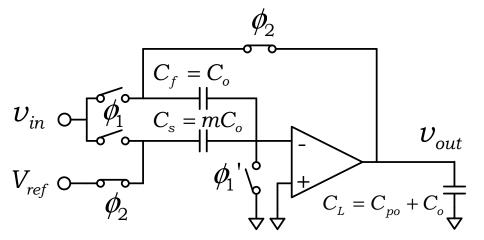

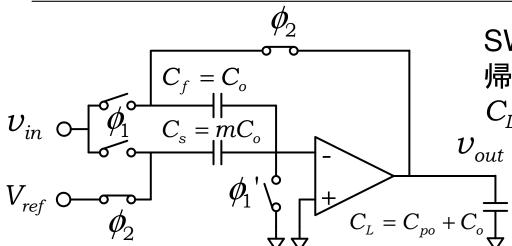

## 3. 解析モデル

解析を行うMDAC

MDACの小信号等価回路

- ●高速化・低消費電力化のため Switched OpAmp技術を使用 →次段のサンプリングSW削除

- ●マルチビットMDACを考慮 *M* bit/stage MDACの場合

$$G_{MDAC} = 2^{M} = m + 1$$

$$C_{L} = C_{po} + C_{o}$$

$|r_{

m s}$ : リファレンスSW ON抵抗

$|r_{\scriptscriptstyle f}:$  フィードバックSW ON抵抗

$C_o$ : 単位容量

$|C_{pi}|$ : OpAmp入力寄生容量

$C_{po}$ : OpAmp出力寄生容量

$g_m$ : OpAmp入力トランジスタ

トランスコンダクタンス

$|r_{L}: \mathrm{OpAmp}$ 出力抵抗

$|\pmb{\omega}_{\scriptscriptstyle p2}$ :OpAmp 第2ポール

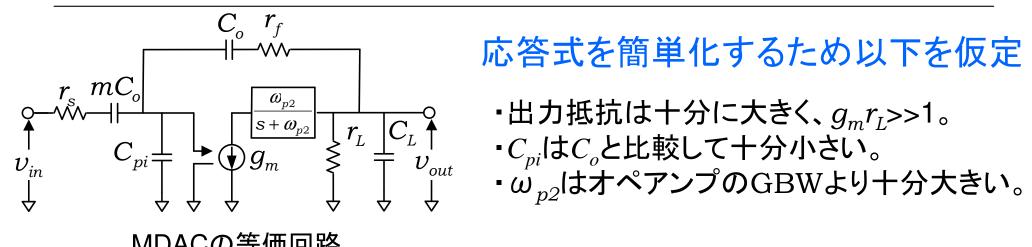

### 4. MDACの応答式

MDACの等価回路

#### 応答式を簡単化するため以下を仮定

#### 伝達関数

$$v_{out} = -\frac{s + z_1}{(s + p_1)(s + p_2)}v_{in}$$

ポール・ゼロ

$$z_1 = \frac{g_m}{C_o(-1 + g_m r_f)}$$

$$p_1 = \alpha - \sqrt{\alpha^2 - \frac{g_m}{mC_oC_L(r_s + r_f)}}$$

$$p_2 = \alpha + \sqrt{\alpha^2 - \frac{g_m}{mC_oC_L(r_s + r_f)}}$$

### MDACのステップ応答式

$$v_{out} = -mV_{in} \left[ 1 - (\cosh \beta t + \gamma \sinh \beta t) e^{-\alpha t} \right]$$

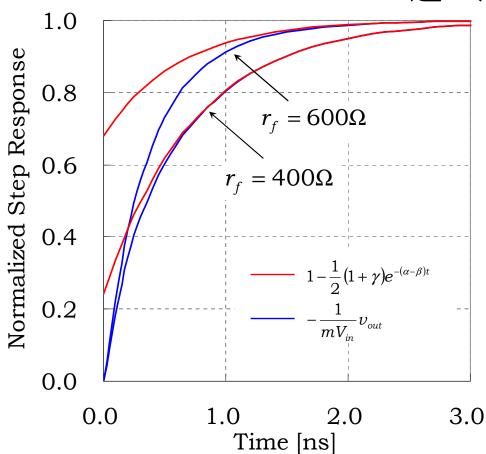

## 5. MDACのステップ応答

$$v_{out} = -mV_{in} \left[ 1 - \frac{1}{2} (1 + \gamma) e^{-(\alpha - \beta)t} - \frac{1}{2} (1 - \gamma) e^{-(\alpha + \beta)t} \right]$$

#### 遅い成分

#### 速い成分

### **Step Response of the MDAC.**

#### **Model Parameter**

| m | $r_s$ | $g_m$  | $C_{o}$ | $C_{pi}$ | $C_{po}$ |

|---|-------|--------|---------|----------|----------|

| 3 | 100 Ω | 11.4mS | 1pF     | 114fF    | 270fF    |

リンギングが起きない場合  $\alpha > 0, \beta > 0, \alpha > \beta$

$$\alpha - \beta < \alpha + \beta$$

ステップ応答は第2項でほとんど決まる。

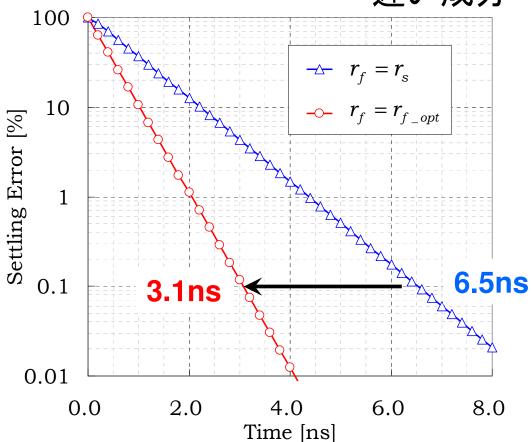

## 6. スイッチON抵抗の最適化

$$v_{out} = -mV_{in} \left[ 1 - \frac{1}{2} (1 + \gamma) e^{-(\alpha - \beta)t} - \frac{1}{2} (1 - \gamma) e^{-(\alpha + \beta)t} \right]$$

### 遅い成分

### MDACのセトリング誤差特性

#### 速い成分

セトリングを速めるには 第2項を小さくすれば良い。

$$(1+\gamma)=0$$

となるON抵抗の条件は

$$r_{f\_opt} = mr_{s} + \frac{(m+1)}{g_{m}}$$

$$v_{out\_opt} = -mV_{in} \left(1 - e^{-\frac{g_m}{(m+1)C_L}t}\right)$$

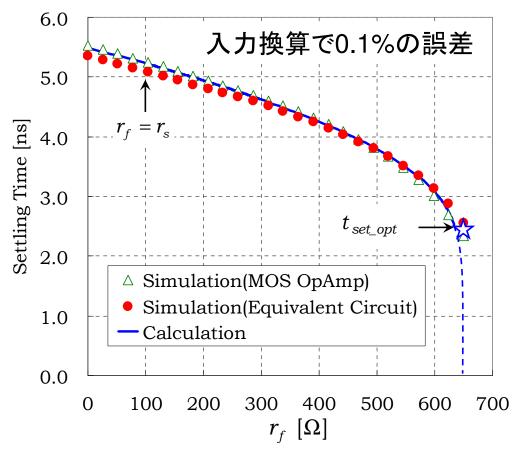

## 7. MDACのセトリング時間

$$v_{out} = -mV_{in} \left[ 1 - \frac{1}{2} (1 + \gamma) e^{-(\alpha - \beta)t} - \frac{1}{2} (1 - \gamma) e^{-(\alpha + \beta)t} \right]$$

### 遅い成分

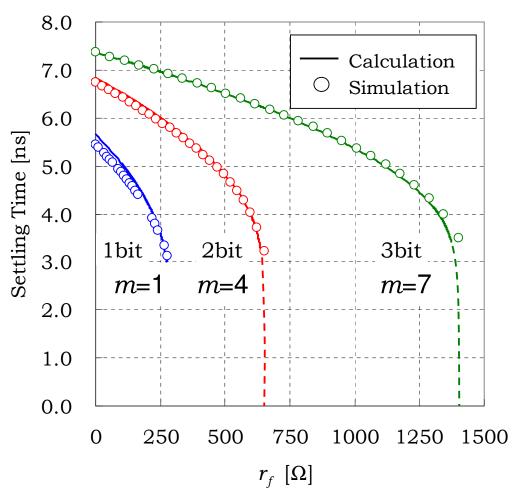

フィードバック抵抗 $r_f$  vs. セトリング時間

### 速い成分

$V_{err}$ :出力許容誤差

a)

$$r_f < r_{f\_opt}$$

$e_o: \frac{V_{err}}{V_{in}}$

$$t_{set} pprox rac{1}{lpha - eta} \ln \left[ rac{1}{2e_o} rac{(m + \gamma)}{m}

ight]$$

b)

$$r_f = r_{f\_opt}$$

$$t_{set\_opt} = \frac{(m+1)C_L}{g_m} \ln \left(\frac{1}{e_o}\right)$$

Sim,Calは5%以内で一致

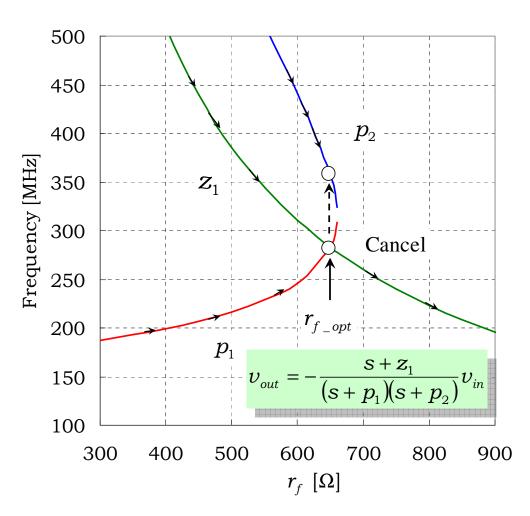

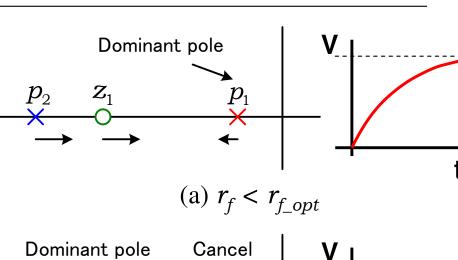

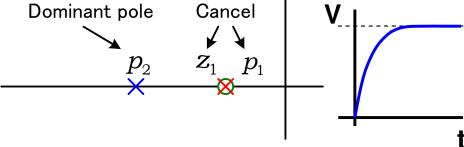

## 8. ポール・ゼロ解析

第1ポールとゼロがキャンセルし、主要極が第2ポールにシフトする。

Pole-zero vs. フィードバック抵抗 $r_f$

(c)

$$r_f = r_{f\_opt}$$

## 発表内容

- 1. 背景•目的

- 2. SWのON抵抗がMDACの性能へ与える影響

- ●解析モデル・応答式の導出

- ●スイッチON抵抗のセトリングへの影響

- ●スイッチON抵抗の最適化

- ●ポール・ゼロ解析

- 3. マルチビットMDACの性能解析

- ●小信号解析(Slewingを含まない場合)

- ●大信号解析(Slewingを含む場合)

- 4. まとめ

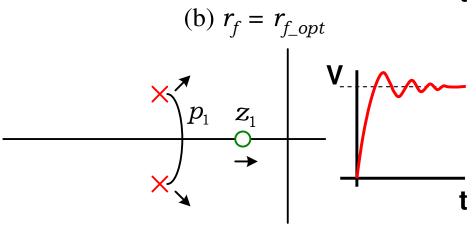

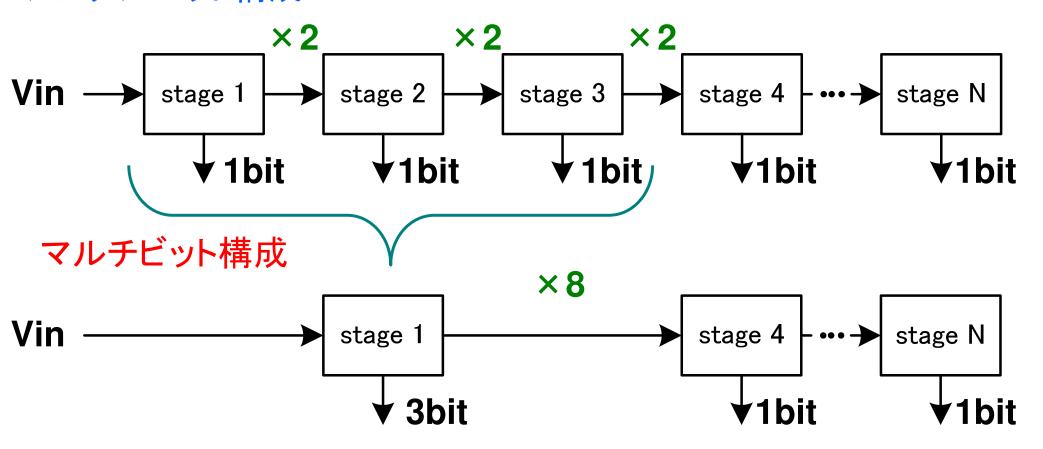

## 9. Pipelined ADC MDACのマルチビット化

- ●ステージ数削減により低消費電力化、省面積。

- ●1ステージあたりのゲインが上がるため、速度が懸念事項。

#### シングルビット構成

### 10. Multi-bit MDAC

- ●MDACをマルチビット化したときにSWのON抵抗が与える影響は?

- ●MDACは何ビット構成が有利なのか?

#### **Model Parameter**

| m        | r <sub>s</sub> | $g_m$  | $C_{pi}$ | $C_{po}$ |

|----------|----------------|--------|----------|----------|

| $2^M$ -1 | 100 Ω          | 11.4mS | 114fF    | 270fF    |

- 1. サンプリング容量 $(m+1)C_o$ を一定とする。

- 2. 次段の容量は

次段のサンプリング容量 =

$$\frac{$$

前段のサンプリング容量  $= C_o$

3. 出力許容誤差は入力換算で等しくなるように (m+1)倍ずつ大きくなる。

### 11. 小信号解析

- ●スルーイングが生じない場合を仮定。

- ●セトリング時間は入力換算で12bit、1LSB以内に収まる時間。

セトリング時間 vs. フィードバック抵抗

$$r_f$$

$$r_{f\_opt} = mr_{s} + \frac{(m+1)}{g_{m}}$$

3bit構成時

$$r_f = r_s$$

7.2 ns  $r_f = r_{f\_opt}$  50%低減

mが大きいほうが $r_f$ に 対する感度が小さい。

多ビット構成のほうが SW最適効果を出しやすい。

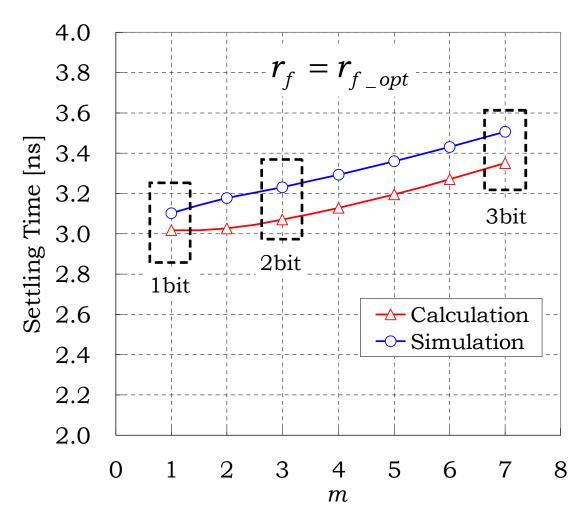

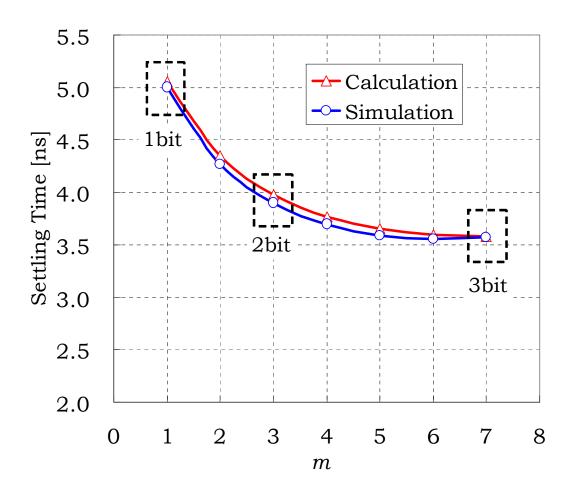

## 12. SW最適条件時のセトリング時間

m=1の時と比較してm=7では10%程度セトリング時間が増加。オペアンプの出力寄生容量次第で増減値は変化する。

か増えると・・・

$$t_{set\_opt} = \frac{(m+1)C_L}{g_m} \ln \left(\frac{1}{e_o}\right)$$

$$C_L = C_{po} + C_o$$

$C_{po}$ が支配的になるとmが増えても $C_L$ は下がらなくなる。

最適セトリング時間 vs.  $m (m=C_s/C_f)$

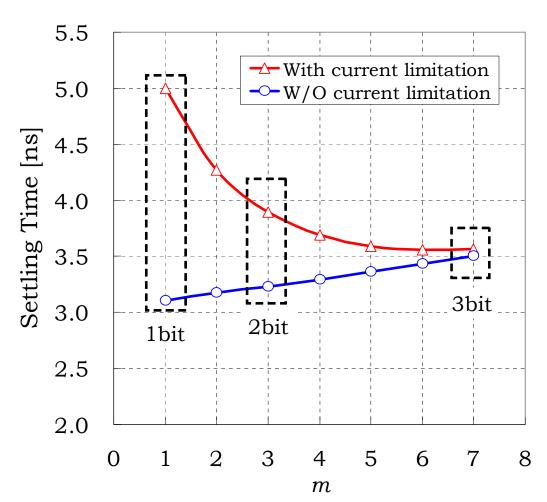

## 13. 大信号解析

- ●スルーイングが生じる場合を想定。

- ●電流制限=1mA, 出力信号振幅=1V(single)、 $r_f = r_{f\_opt}$ を仮定。

多ビットになるほどスルーイングの 影響が小さくなる。

多ビット構成では

- 1)出力負荷容量が小さい。

- 2)フィードバックファクターが小さい。 ため、スルーイングの観点からは有利。

スルーイングを含むセトリング時間 vs.  $m (m=C_s/C_f)$  Simulation 結果

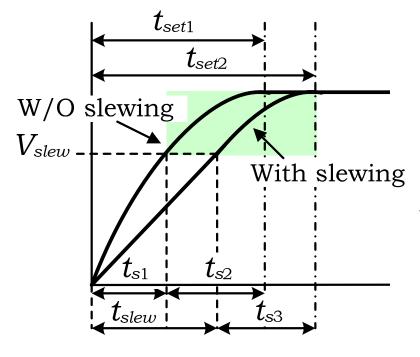

### 14. スルーイングを含むセトリング時間の導出

スルーイングが終わってからの応答は、 スルーイングがない時の応答と同じ応答をすると 仮定してセトリング時間の近似値を導く。

$$t_{set1} = \frac{(m+1)C_L}{g_m} \ln \left(\frac{1}{e_o}\right)$$

スルーイングがない場合の傾きとスルーレートが等しくなる時間 $t_{s1}$ は

$$\begin{aligned} t_{s1} &= \frac{(m+1)C_L V_{eff}}{g_m} \ln \left[ \frac{(m+1)C_L V_{eff}}{2mC_{eff} V_{in}} \right] \\ t_{s2} &= t_{set1} - t_{s1} \approx t_{s3} \end{aligned}$$

スルーイングが終了するときの出力電圧は、

$$V_{slew} = -mV_{in} \left(1 - e^{-\frac{g_m}{(m+1)C_L}t_{s1}}\right)$$

スルーイングが終了するときの時間は

$$t_{slew} = \frac{C_{eff}}{I_{bias}} V_{slew}$$

$$t_{set2} \approx t_{slew} + t_{s3}$$

$$g_m \approx \frac{2I_{bias}}{V_{off}}$$

:トランスコンダクタンス

$$SR = \frac{I_{bias}}{C_{eff}}$$

:スルーレート

$$C_{eff} pprox C_L + rac{C_s C_f}{C_s + C_f}$$

: 実効負荷容量 スルーイングを含んだ場合のセトリング時間は

### 15. スルーイングを含むセトリング式の評価

#### 5%以内でシミュレーション結果と一致。

スルーイングを含むセトリング時間 vs.  $m (m=C_s/C_f)$  Simulationと計算結果

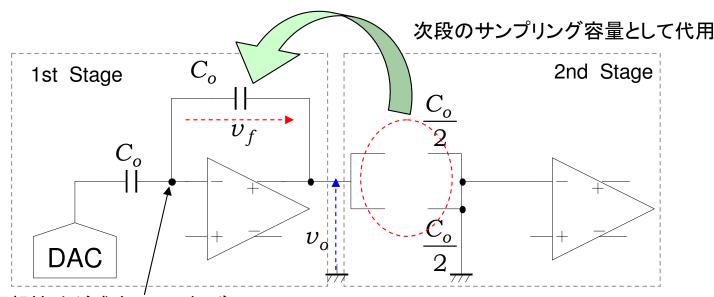

## 16. SWの最適化を生かすMDAC構成

SW条件が最適であればセトリング時間は帰還容量、ON抵抗に依存しない。 $C_L$ を小さく出来ればよい。

$$t_{set\_opt} = \frac{(m+1)C_L}{g_m} \ln \left(\frac{1}{e_o}\right)$$

仮想接地が成立していれば

$$v_f = 2v_{in} - v_{dac}$$

$$v_o = 2v_{in} - v_{dac}$$

負荷容量が極めて小さくなる Loading Free Architecture

### 17. まとめ

- 1. SWのON抵抗がMDACの性能に与える影響を明らかにした。 SWのON抵抗の変化に対するポール・ゼロの動きからセトリングの形状、 セトリング時間の変化、セトリング時間最適化のメカニズムを示した。

- 2. セトリング時間を最短にするSWのON抵抗条件を導出した。

$$r_{f\_opt} = mr_s + \frac{(m+1)}{g_m}$$

$$r_f = r_s$$

$$7.2 \text{ ns}$$

$$r_f = r_{f\_opt}$$

$$3.5 \text{ ns}$$

50%低減 (3bit構成)

3. SWの最適化を生かすMDACの構成について考察した。

SWの最適化の効果の出しやすさ、スルーイングを含めた時のセトリング時間を考えるとマルチビット化した方が速度、消費電力の面で有利な場合がある。また、Loading Free Architectureを用いた場合は効果がでやすい。

### 今後の課題

SWのON抵抗入力依存性を考慮した上で 実設計に取り込む方法について考える。

### 謝辞

本研究は(株)半導体理工学研究センター (STARC)の支援を受けて実施されたものである。

ここに感謝の意を表する。

## 参考資料

## 式の詳細

$$v_{out} = \frac{s + z_1}{(s + p_1)(s + p_2)}$$

$$z_1 = \frac{g_m}{C_o(-1 + g_m r_f)}$$

$$z_{1} = \frac{g_{m}}{C_{o}(-1 + g_{m}r_{f})} \qquad p_{1} = \alpha - \sqrt{\alpha^{2} - \frac{g_{m}}{mC_{o}C_{L}(r_{s} + r_{f})}} \qquad p_{2} = \alpha + \sqrt{\alpha^{2} - \frac{g_{m}}{mC_{o}C_{L}(r_{s} + r_{f})}}$$

$$p_2 = \alpha + \sqrt{\alpha^2 - \frac{g_m}{mC_oC_L(r_s + r_f)}}$$

$$v_{out} = -mV_{in} \left[ 1 - \frac{1}{2} (1 + \gamma) e^{-(\alpha - \beta)t} - \frac{1}{2} (1 - \gamma) e^{-(\alpha + \beta)t} \right]$$

$$\alpha = \frac{mC_o(1 + g_m r_s) + C_L(m + 1)}{2mC_oC_L(r_s + r_f)} \qquad \beta = \sqrt{\alpha^2 - \frac{g_m}{mC_oC_L(r_s + r_f)}} \qquad \gamma = \frac{1}{\beta} \left( \alpha + \frac{1 - g_m r_f}{mC_L(r_s + r_f)} \right)$$

# スルーイング込みのセトリング時間

$$t_{set1} = \frac{(m+1)}{g_m} \ln \left[ \frac{1}{e_o} \right]$$

$$t_{s1} = \frac{(m+1)}{g_m} \ln \left[ \frac{(m+1)C_L V_{eff}}{2mC_{eff} V_{in}} \right]$$

$$t_{s3} \approx t_{set1} - t_{s1} = \frac{(m+1)C_L}{g_m} \ln \left[ \frac{2mC_{eff}V_{in}}{e_o(m+1)C_LV_{eff}} \right]$$

$$V_{slew} = -mV_{in} \Biggl( 1 - e^{-rac{g_m}{(m+1)C_L}t_{s1}} \Biggr) = -mV_{in} \Biggl[ 1 - rac{2mC_{eff}V_{in}}{(m+1)C_LV_{eff}} \Biggr]$$

— ※式の変形時に $rac{(m+1)C_LV_{eff}}{2mC_{eff}V_{in}}$ の正負に注意。

$$t_{slew} = \frac{C_{e\!f\!f}}{I_{bias}} V_{slew} = -\frac{mC_{e\!f\!f} V_{in}}{I_{bias}} \left[ 1 - \frac{2mC_{e\!f\!f} V_{in}}{(m+1)C_L V_{e\!f\!f}} \right]$$

$$t_{set2} \approx t_{slew} + t_{s3} = -\frac{mC_{eff}V_{in}}{I_{bias}} \left[ 1 - \frac{2mC_{eff}V_{in}}{(m+1)C_{L}V_{eff}} \right] + \frac{(m+1)C_{L}}{g_{m}} \ln \left[ \frac{2mC_{eff}V_{in}}{e_{o}(m+1)C_{L}V_{eff}} \right]$$