# 微細・低電圧デバイスの課題と デジタルアーキテクチャへの期待

東京工業大学 大学院理工学研究科 電子物理工学専攻

松澤昭

### 内容

- ワイアレスシステムの動向

- · パイプライン型ADC

- · 微細化CMOSデバイスとアナログ特性

- ・ 低電圧動作とアナログ回路性能

- ΣΔ型ADC: 高精度化へのシステム的アプローチ

- ・ 今後の方向性

- ・まとめ

# ワイアレスシステムの動向

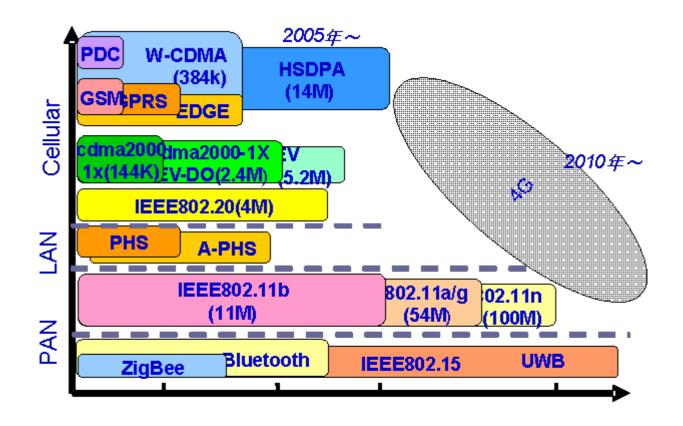

### ワイアレスシステムの多様化

今後増大するワイアレスシステムの規格 LSIの開発を合理的に進める必要がある。

データの下り最高伝送速度

### マルチスタンダード化

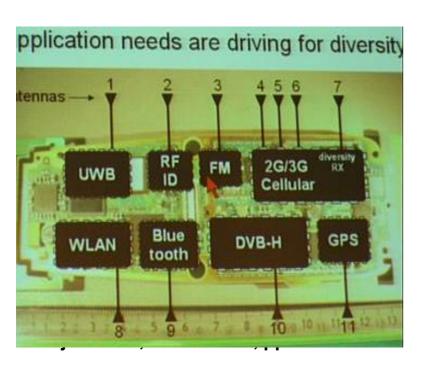

#### たくさんのワイアレス規格を携帯に実装する必要が出てくる

# Future cellular phone needs 11 wireless standard!!

#### Multi-standards and multi chips

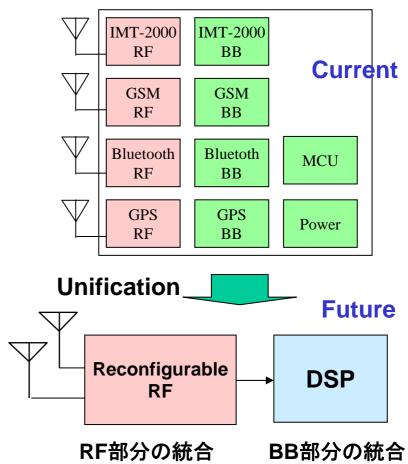

#### チップ構成の方向

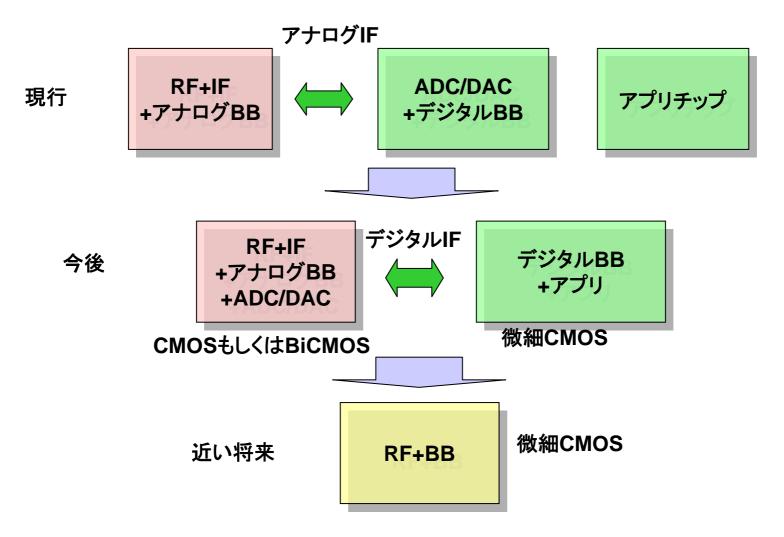

#### ADC, DACを含むアナログRF回路がSoCに全て集積される方向

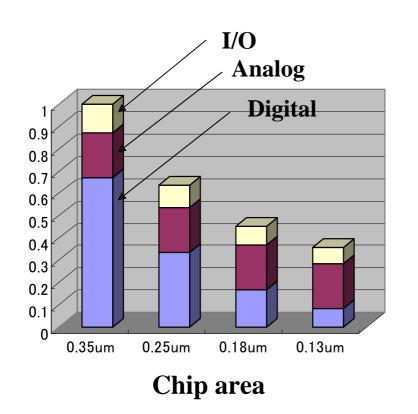

#### アナログ部のコストの増大

アナログ・RF回路は面積縮小が困難である。このため微細化が進むとアナログ回路はコストが増大する。したがって今後はできるだけアナログ・RF回路を抑えるアーキテクチャが必要となる。

### RF CMOSチップのSoC化

RF CMOSチップはアナログリッチからデジタルリッチのSoCになっていくだろう。

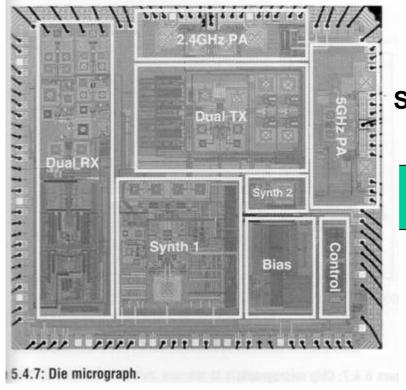

#### Wireless LAN, 802.11 a/b/g

0.25um, 2.5V, 23mm<sup>2</sup>, 5GHz

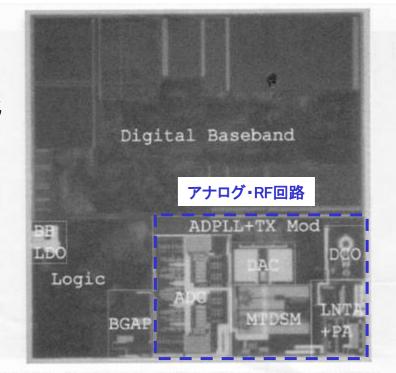

#### **Discrete-time Bluetooth**

0.13um, 1.5V, 2.4GHz

SoC化

jure 15.1.7: Die micrograph of the single-chip Bluetooth transceiver.

K. Muhammad (TI), et al., ISSCC2004, pp.268

M. Zargari (Atheros), et al., ISSCC 2004, pp.96

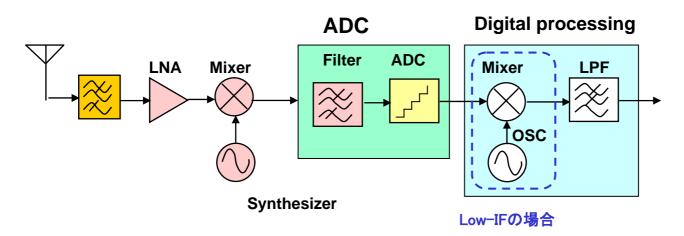

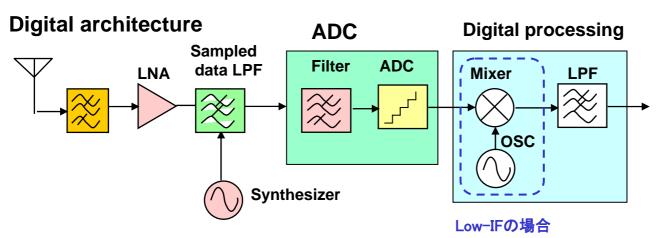

#### 今後のアーキテクチャ

アナログ回路をできるだけデジタル回路に置き換える方向 ADCの開発が鍵になる。

K. Muhammad (TI), et al., ISSCC2004, pp.268

#### ワイアレスシステム用ADC

### 第4世代携帯電話

第4世代携帯電話まだはっきりしていないが以下のような特徴になりそうである。

- 超高速データ伝送

- 100Mbps:移動環境 1Gbps:屋内

- 空間並列のMIMOの利用

- MIMOシステムにより超高速データ通信を可能にする

- MIMOは4チャネル、したがって1チャネルあたり250Mbps

- 変復調はOFDMを使用

- キャリア周波数は 携帯電話としては0.8GHZから2.5GHzであまり変わらない。W-LAN対応として5GHz対応になる。

- マルチスタンダードへの対応が必要

- ソフトウエア無線技術の大幅導入

- 微細CMOS (60nm~45nm?)を用いる。大きな理由はOFDMとMIMOに必要な大規模デジタル演算が不可欠なため。

#### 第4世代携帯電話に向けたアナログ回路技術

もっとはっきりしていないが以下のようなことを考える必要がある。

- 超高速データ伝送

- ADCの高速化 10b, 400MHz程度は必要か?

- ADCの低電力化:携帯端末に搭載可能

- Filterの広帯域化

- マルチスタンダードへの対応 ソフトウエア無線技術の大幅導入

- ADCの性能可変化 (GSMなどの高ダイナミックレンジにも対応?)

- シンセサイザ・PLL特性の可変化

- 微細CMOSでのアナログ回路のオンチップ化

- 65nm以下のプロセスでの低電圧アナログ回路技術の確立

- ノイズ・クロストークの抑制

# パイプライン型ADC

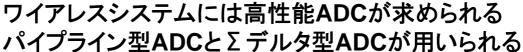

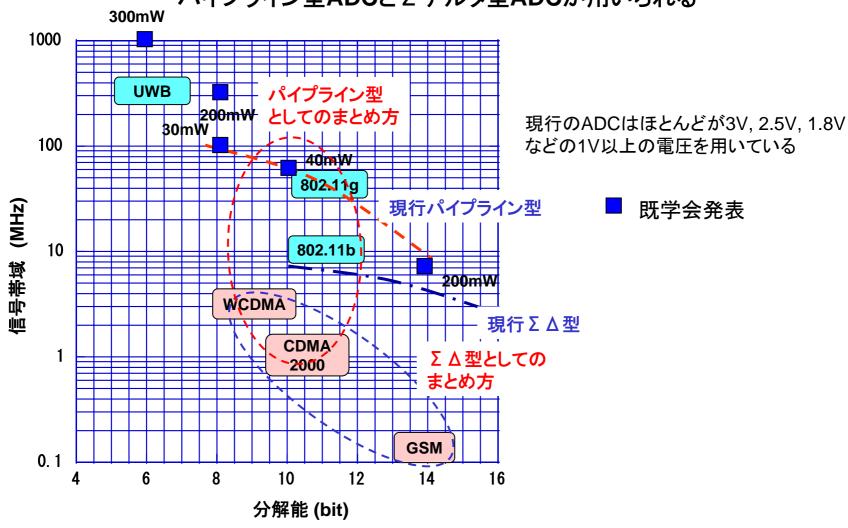

#### 高速・高分解能ADCの電力と周波数

#### 高速化・高ダイナミックレンジになるほど大きな消費電力を必要とする

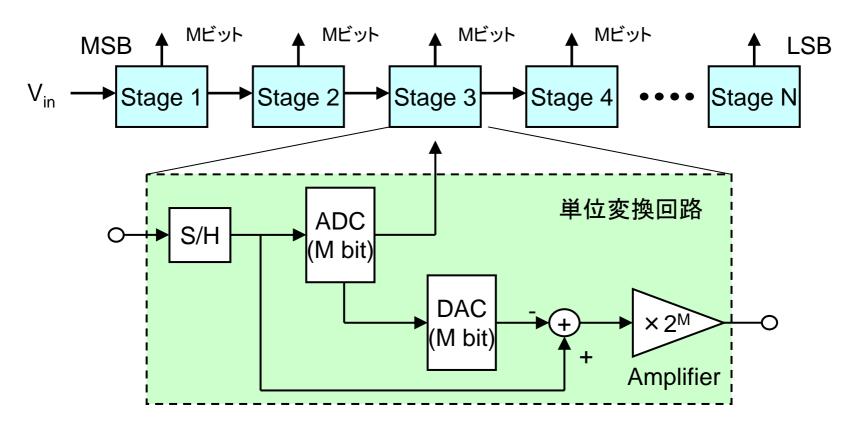

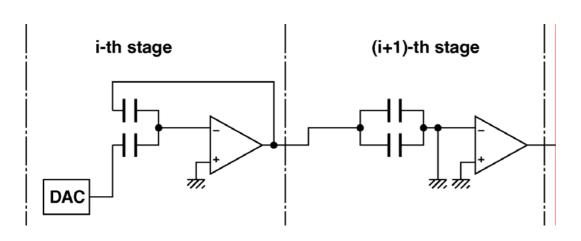

### パイプライン型ADC:構成

- 単位変換回路を縦続接続

- ・各単位変換回路は入力信号を標本化し、参照電圧と比較を行いMビットの変換

- ・ADCの出力により、DACが出力する電圧が変化。入力信号とDACの出力する 電圧の差分を2<sup>M</sup>倍して後段に出力。

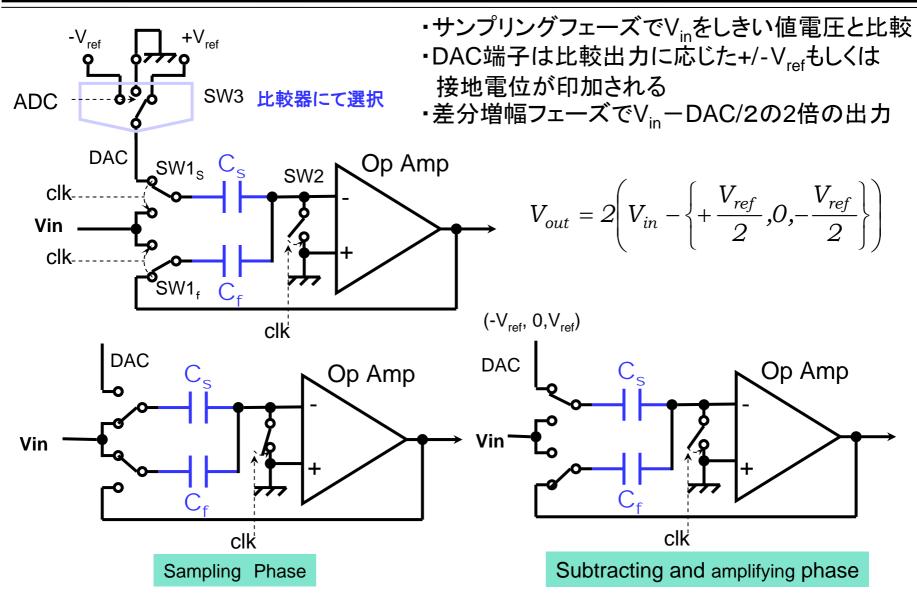

### パイプライン型ADC:単位回路

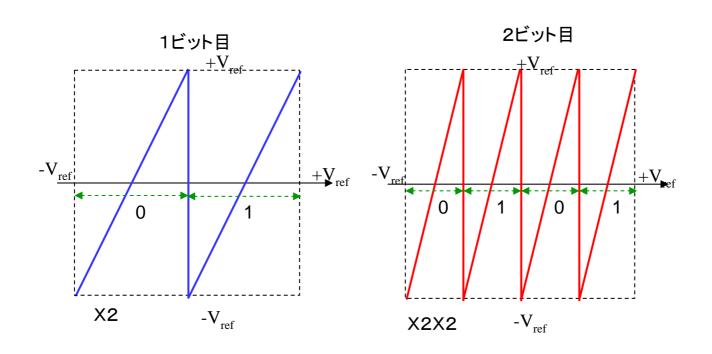

### パイプラインADC:回路動作

#### 信号を折れ返して転送することにより1ビットずつの変換を行う

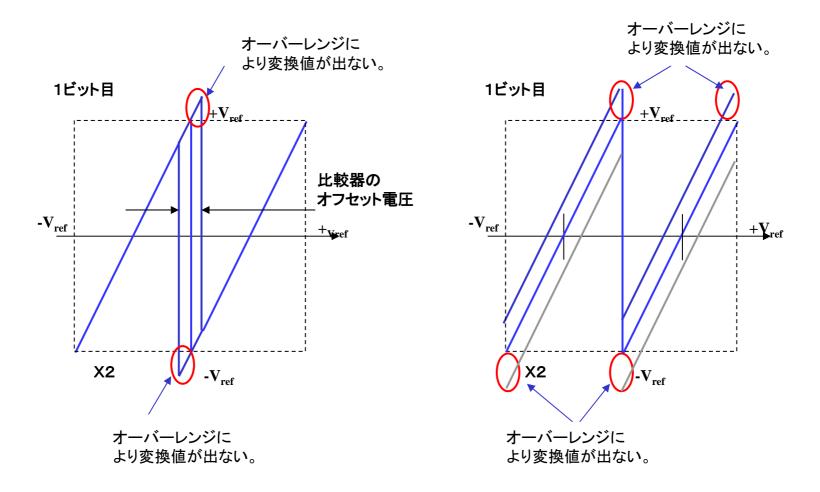

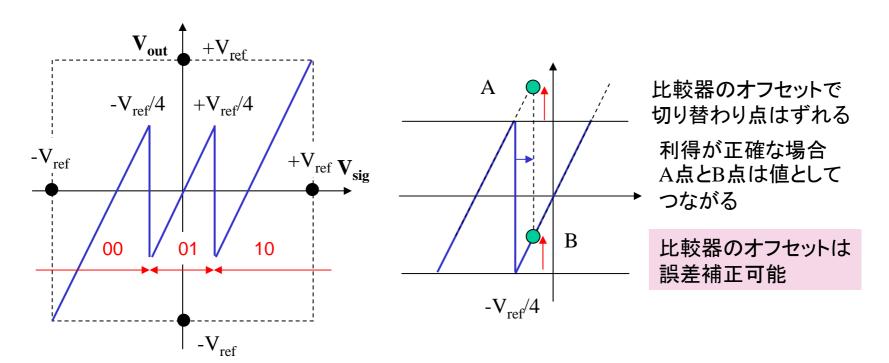

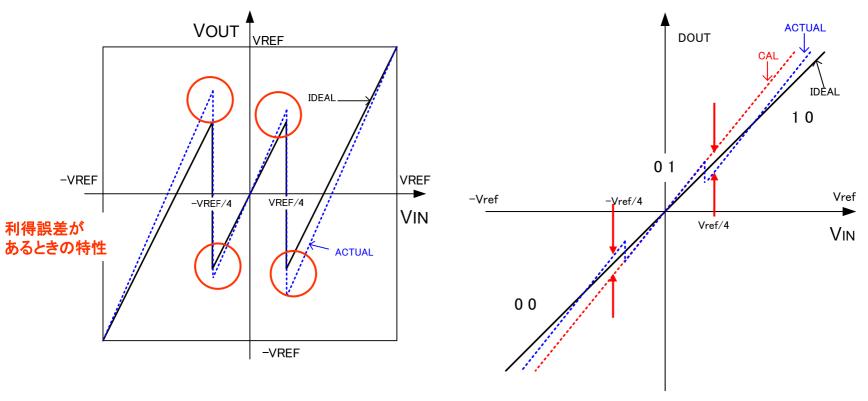

### 比較器とOPアンプのオフセット電圧の影響

単純な折れ返し転送では比較器やOPアンプのオフセット電圧によりA/D変換電圧範囲を 逸脱し、信号変化が変換値に反映されない状態になる。

#### 1.5ビット冗長型パイプライン型ADC

比較器を2個設けて+/- V<sub>ref</sub>/4の電圧で折れ返すようにしたのが1.5ビット冗長構成である。 この構成により比較器やOPアンプのオフセットが発生しても変換電圧範囲に留まり、変換値自 体は連続しているため誤差のない変換が可能となった。

#### 1.5ビット冗長構成

理想変換特性

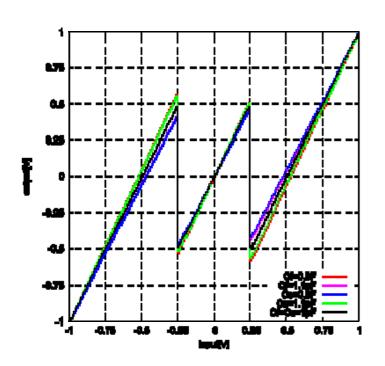

#### 容量ミスマッチがあるときの変換

容量ミスマッチがあるときの変換では各段の比較器の切り替え点で大きな誤差が発生する

初段の増幅器の入出力電圧特性

A/D変換器の入出力特性

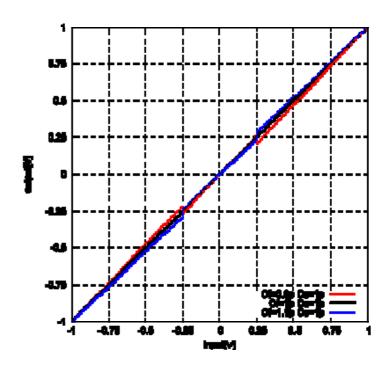

### 容量ミスマッチ精度

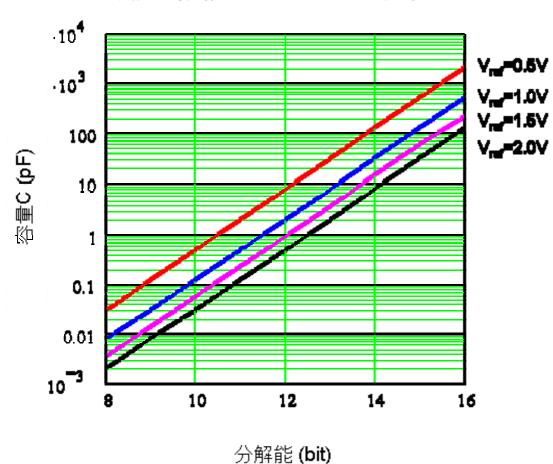

容量ミスマッチからは分解能が2ビット上がる毎に必要容量は1桁上昇する

2005.06.21 A. Matsuzawa, Titech

### 誤差補正

利得誤差があると変換誤差を生じるが、この誤差を計測して引くことにより補正可能であるしたがって、容量ミスマッチはあまり考慮しなくてもよくなった。

1.5Bステージの変換特性

ADC入出力特性

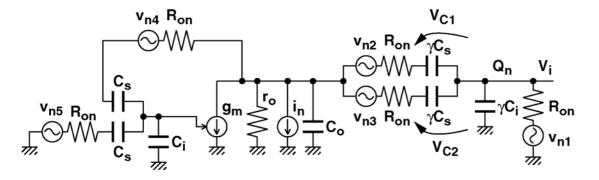

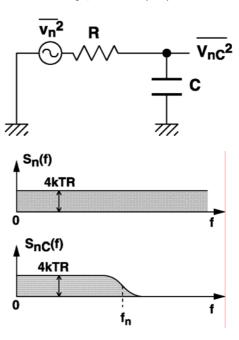

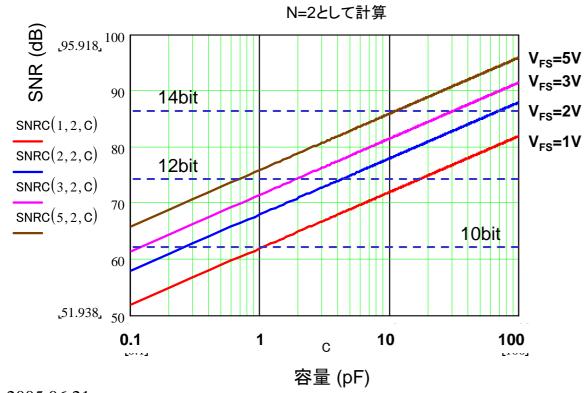

# 精度を決めるもの:ノイズ

最終的にADCの精度を決めるものはノイズである。 トランジスタ・抵抗などいくつかのノイズ源があるが、最終的には容量で決定される。

静岡大 川人先生より

$$\overline{v_{nC}^{2}} = 4kTR \int_{0}^{\infty} \frac{1}{1 + (\omega/CR)^{2}} df$$

$$= \frac{kT}{C}$$

### ノイズの計算

信号電力とノイズ電力の比がSNRである。高分解能になるほど高いSNRが求められる。 ノイズ電力は容量で決定され、信号電力は信号振幅で決定される。

a)kT/Cノイズ

b)入力換算熱雑音

全ノイズ

$$v_{c_{-}tot}^{2} = \sum_{n=0}^{N-1} \frac{1}{2^{n}} \frac{kT}{C} \approx \frac{2kT}{C}$$

$v_{ther}^{2} \approx 1.7 \frac{kT}{C}$   $v_{c_{-}tot}^{2} + v_{ther}^{2} \approx 3.7 \frac{kT}{C}$

このノイズ電力が量子化ノイズ電力の半分であることが必要を基準とすると、

$$\begin{split} v_q^2 &= \frac{1}{3} \left( \frac{q}{2} \right)^2 = \frac{1}{3} \left( \frac{2V_{ref}}{2^{N+1}} \right)^2 = \frac{V_{ref}^2}{3 \cdot 2^{2N}} \\ v_{c\_tot}^2 &+ v_{ther}^2 \approx 3.7 \frac{kT}{C} \text{ (T=400K)} \end{split}$$

$$C(pF) \ge 1.23 \times 10^{-7} \left(\frac{2^N}{V_{ref}}\right)^2$$

の条件が得られる。

#### 分解能と信号振幅および容量

kT/Cノイズからは分解能が2ビット上がる毎に必要容量は1桁上昇するまた、信号振幅が減少すると必要容量は減少率の2乗に比例して増加する。

10bit: 0.1pF

12bit: 2pF

14bit: 30pF

10bit: 0.025pF

12bit: 0.5pF

14bit: 8pF

#### 参照電圧の2乗に反比例

$$C(pF) \ge 1.23 \times 10^{-7} \left(\frac{2^N}{V_{ref}}\right)^2$$

V<sub>ref</sub>: 片側振幅

分解能と必要容量

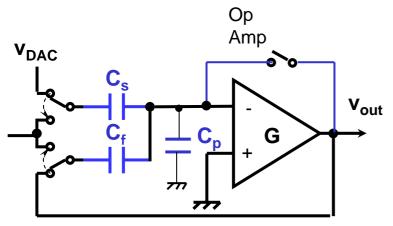

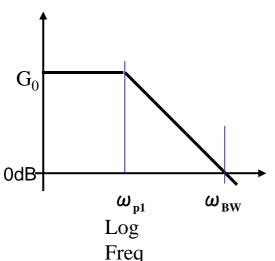

#### オペアンプの利得とGBW

必要なDCゲインは分解能から算出され、NビットADCのSNRに8dB加えたものである。 必要なGBWは変換周波数に分解能を掛けたものである。

$$\begin{split} v_{out} &= 2 \bigg( v_{in} - \frac{v_{DAC}}{2} \bigg) \frac{1}{1 + \frac{1}{G} \bigg( 2 + \frac{C_p}{C_f} \bigg)} \\ G_{error} &\approx -\frac{1}{G} \bigg( 2 + \frac{C_p}{C_f} \bigg) \approx -\frac{1}{G\beta} \\ \end{split} \qquad \frac{1}{G} \leq \frac{\beta}{2^{N-M+1}} \end{split}$$

### G(dB) > 6N + 10 (NE) HADCOSNRIA

SNR=6N+2 (dB)

$$E_{rror} = \frac{1}{1 + G(s)\beta} = \frac{1}{1 + \frac{G_0\beta}{1 + \frac{s}{\omega_{p1}}}}$$

$$E_{rror} = \exp(-G_0\omega_{p1}\beta t) = \exp(-\frac{t}{\tau}), \ \tau = \frac{1}{\omega_{BW}\beta}$$

$$\exp(-\frac{t_{ss}}{\tau}) < \frac{1}{2^{N-M+1}} \qquad GBW > N \cdot f_0$$

$$\exp(-\frac{t_{ss}}{\tau}) < \frac{1}{2^{N-M+1}}$$

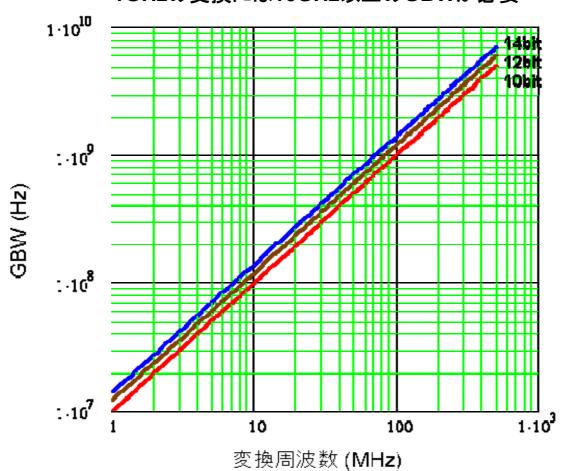

### オペアンプのGBW

#### OPアンプのGBWは変換周波数のおよそ10倍から15倍程度必要

#### →1GHzの変換には10GHz以上のGBWが必要

$t_{ss}$ は変換の半周期の2/3  $\beta$  =1/3としたとき

A. Matsuzawa, Titech

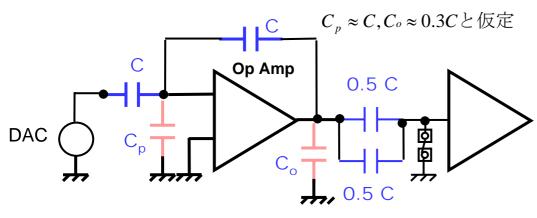

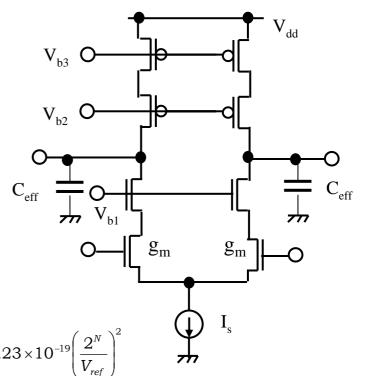

### OPアンプの動作電流計算

次段の容量は半分にできる

OPアンプの実効負荷容量

$$C_{eff} \approx 2(0.5C) + \frac{2}{3}C + 0.3C \approx 2C$$

$$GBW \approx \frac{g_m}{2\pi C_{eff}} \approx \frac{g_m}{4\pi C} \approx \frac{I_s}{4\pi C V_{eff}} \approx \frac{I_s}{2.5C} \qquad C \ge 1.23 \times 10^{-19} \left(\frac{2^N}{V_{ref}}\right)^2$$

N:分解能 GBW=Nfcを用いると fc=変換周波数

$$I_s \approx 2.5C \cdot N \cdot f_c$$

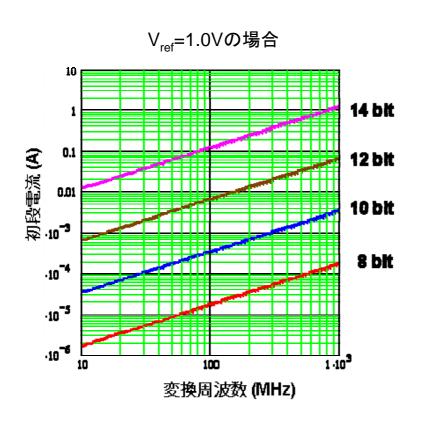

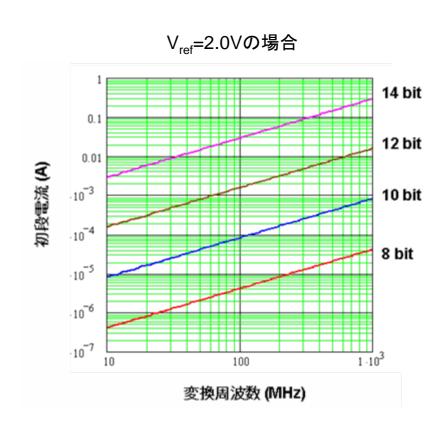

$$\therefore I_s \geq 3.1 \times 10^{-19} \times \frac{N \cdot 2^{2N}}{V_{ref}^2} \cdot f_c$$

#### オペアンプの動作電流

分解能が2ビット上がるにつれて約20倍消費電流が増加する。 変換周波数が1桁上がると消費電流も1桁上がる。

信号振幅を2倍に上げると消費電流は1/4になる

# 微細化CMOSデバイスとアナログ特性

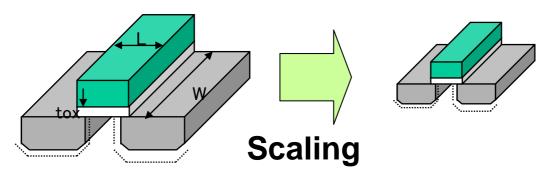

#### スケーリング則

スケーリング則はLSI技術と電子産業の発展の法則である。

小さく・薄く・低電圧にすることでコストが下がり、速度が上がり、低電力になった。

| Device/Circuit parameter    | <b>Scaling Factor</b> |

|-----------------------------|-----------------------|

| Device dimensions L, W, Tox | 1/S                   |

| Doping concentration        | S                     |

| Voltage                     | 1/S                   |

| Field                       | 1                     |

| Current                     | 1/S                   |

| Gate Delay                  | 1/S                   |

| Power dissipation/device    | 1/S <sup>2</sup>      |

$$S \approx \sqrt{2}$$

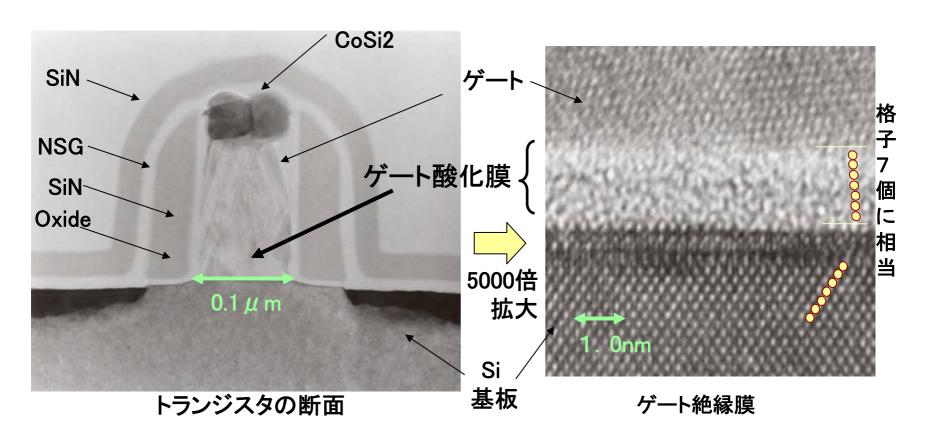

#### 現在のSoC用トランジスタ

現在のSoCの量産プロセスである0.13umルールのトランジスタ原子レベルの制御が求められる。

松下電器

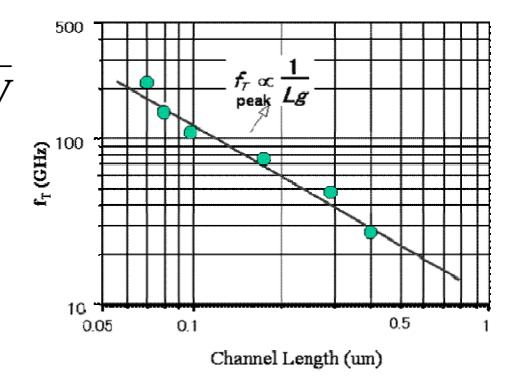

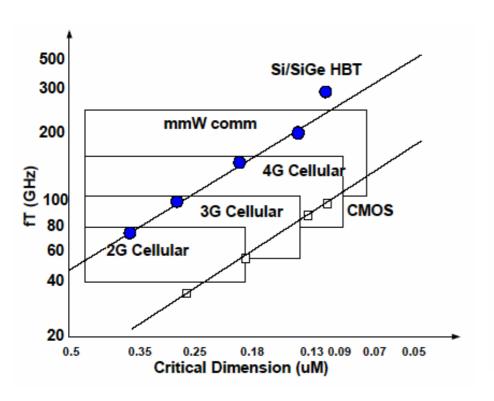

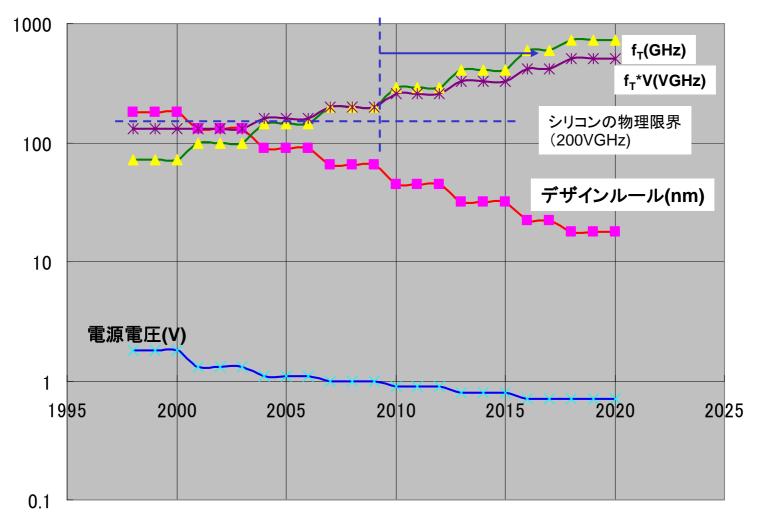

# スケーリングのメリット: frの上昇

#### ピークの遮断周波数はチャネル長に反比例する

高速・広帯域回路の実現には微細化デバイスは不可欠である

$$f_{T} \approx \frac{g_{m}}{2\pi C_{gs}} = \frac{g_{m}}{2\pi C_{ox}LW}$$

$$g_{msat} = WC_{ox}v_{sat}$$

$$\therefore f_{T\_peak} = \frac{v_{sat}}{2\pi L}$$

(0.1umでは120GHz程度に達する)

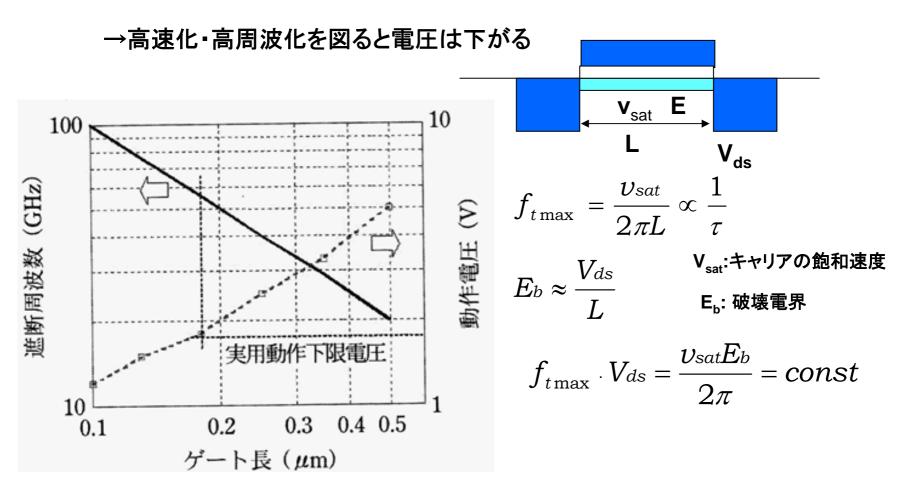

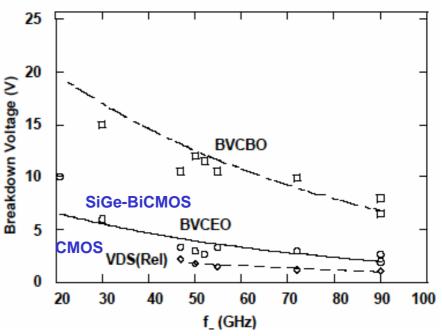

## 高速・高周波化と電源電圧

チャネル長を短くするとキャリアの走行時間が短くなり高速・高周波になる。 一方、破壊電界は物質で決まり、チャネル長が短くなると電界は高くなる。

# frと動作電圧

- ・機器の高周波化に伴い、高いf<sub>T</sub>が必要とされる。

- ・同一ルールではSiGe-BiCMOSが $f_{\tau}$ が高い。ただし適用ルールはCMOSが1.5世代ほど早い

- ・同一f<sub>T</sub>ではSiGe-BiCMOSの方がCMOSよりも2倍程度動作電圧が高い。 (CMOSが低いのはホットキャリアによる劣化が接合ブレークダウンよりも低電圧から起こるため)

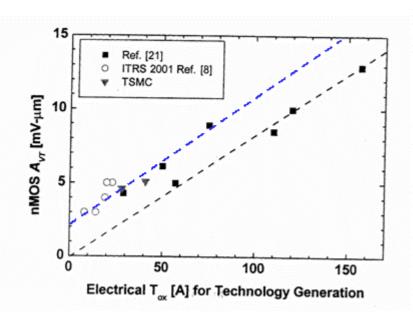

### MOSのV<sub>T</sub>ばらつきと1/fノイズ

#### MOSのV<sub>T</sub>ばらつき係数は飽和する

$$\Delta V_{TH}(mV) \approx \frac{1}{\sqrt{2}} \left( \frac{T_{ox}(nm) + 2}{\sqrt{LW}(\mu m)} \right)$$

#### 1/fノイズ係数は穏やかに減少

$$V_{flick}^{2}(uV^{2}/Hz) = \frac{16T_{OX}^{2}(nm)}{LW(\mu m^{2}) \cdot f(Hz)}$$

C. H. Diaz, et al., "CMOS Technology for MS/RF SoC," IEEE Tran. Electron Devices, Vol. 50, No.3, March, 2003.

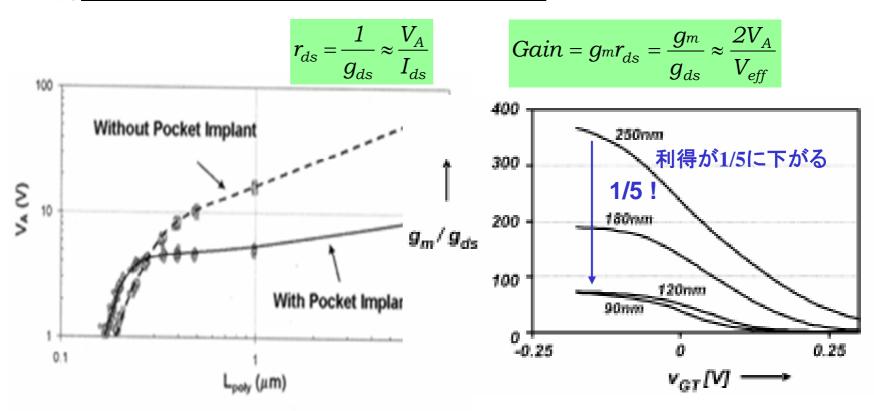

### 微細デバイスのドレイン抵抗

微細デバイスではポケット注入を用いていることにより、 チャネル長を伸ばしてもV<sub>A</sub>つまりはドレイン抵抗はあまり上がらない。 つまり、微細プロセスではDC利得が下がることを意味する。

D, Buss, et al., IEEE, Tran on ED, Vol. 50, pp.546-556, 2003

A.J. Annema, JSC 2005, pp132-143

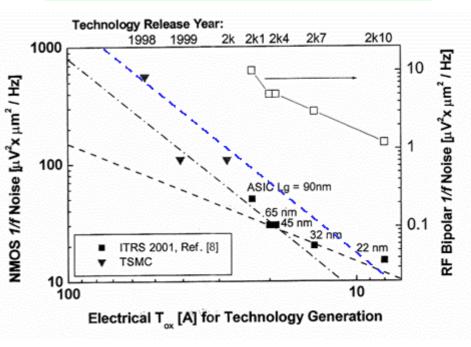

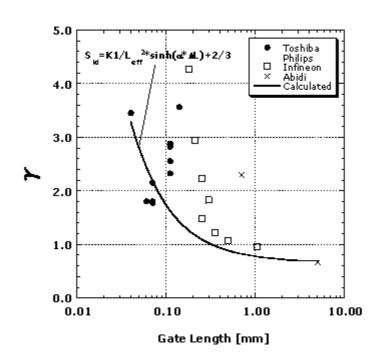

# 微細化とノイズ

微細化とともに熱雑音係数は増大、同じgmでも微細になるとノイズが多くなる

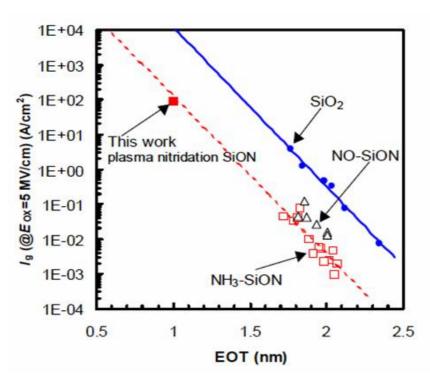

#### ゲート電流

ゲート酸化膜が2nm以下になるころからトンネリングリーク電流が顕著になった。 S&H回路やSCF回路では低速動作の場合にスイッチのリーク電流に注意する必要がある

$EOT = \frac{\mathcal{E}_{SiO2}}{\mathcal{E}} thickness$

EOT (Equivalent Oxide Thickness)等価酸化膜厚

窒化膜の導入で緩和される。

しばらくは凌げる

しかしいずれ高誘電体膜にして物理膜厚を厚くする必要がある

窒化膜は1/fノイズを増加させると言われている。

A. Hokazono et al., IEDM'02, p.639

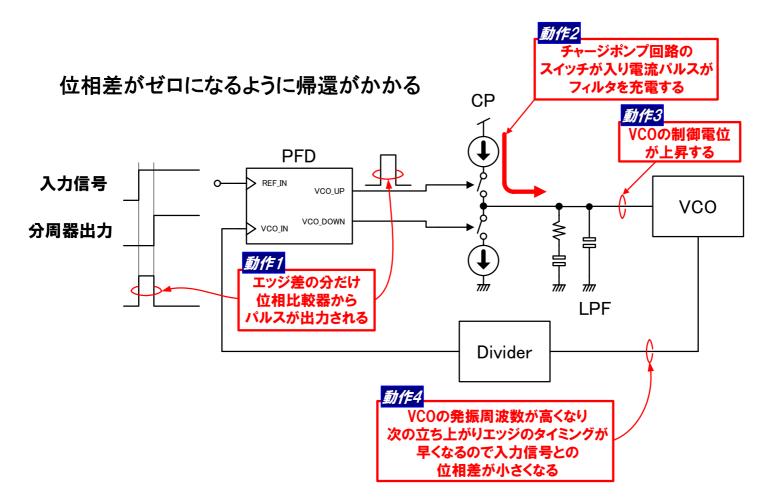

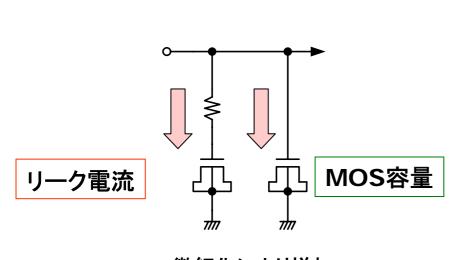

## チャージポンプPLL

現在主流となっているPLL回路はPFDとチャージポンプを用いたものである。

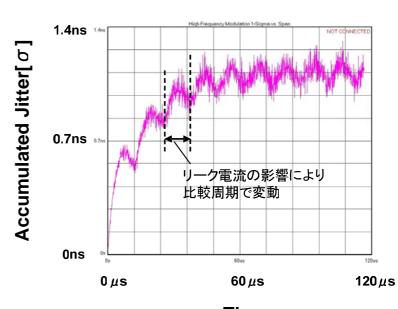

#### PLLにおけるゲートリーク電流課題

PLLは長い時定数が要求され、大きな容量が必要なため今まではゲート容量が使用されてきた。しかしゲートリーク電流があると電荷が抜けてしまい、VCO電圧が下がるのでこれを補償するためにPFD+CPから周期的に信号が出る。これがジッタとなる。今後はゲート容量が使えず、フィルターのデジタル化は進むものと思われる。

微細化により増加 (130nm:1kHz=>65nm:1MHz)

Time アキュームレーションジッタ特性

- 最も単位容量の大きいMOS容量が使えなくなりつつある

- リーク電流の影響でジッタ特性が劣化

- 配線間容量はMOS容量の10倍の面積が必要

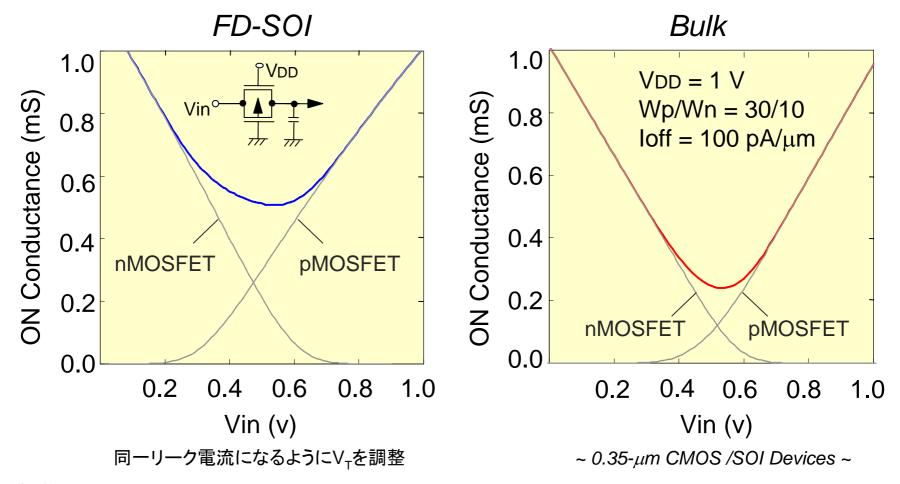

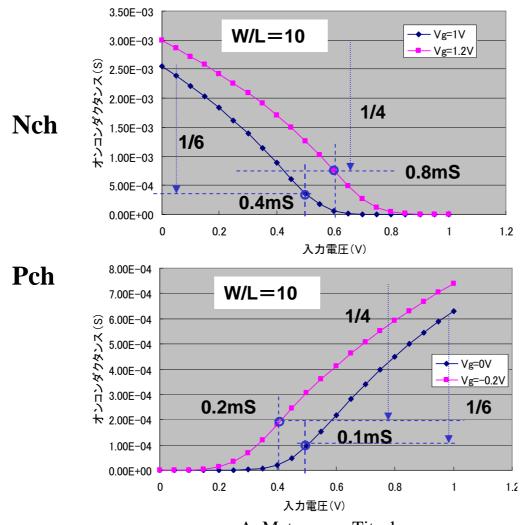

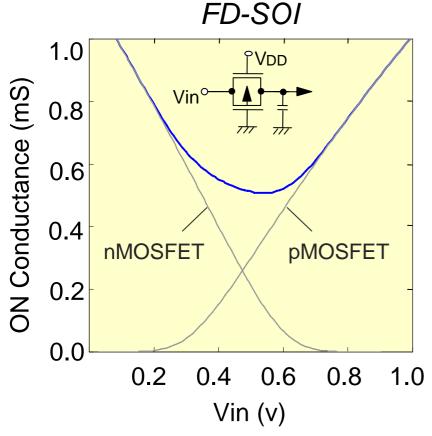

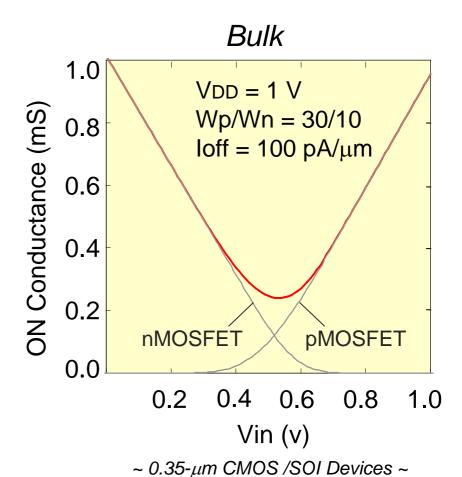

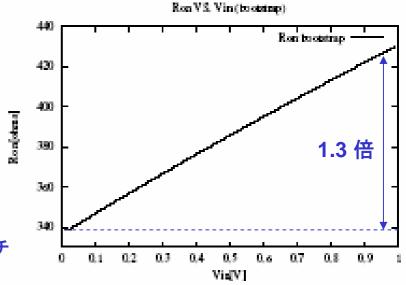

### 低電圧アナログスイッチ特性

- ・低電圧ではオン抵抗が大きな入力電圧依存を持つ(4倍)

- ·SOIはオン抵抗の入力電圧依存性が小さい(2倍)

#### 90nmCMOSのオンコンダクタンス

1V動作ではCMOS スイッチのオン抵抗変化は最大3倍になる。また $V_T$ が0.1V高いとオンしない。 低電圧で良好なスイッチ特性の実現のための開発が不可欠である。

# 低電圧動作とアナログ回路性能

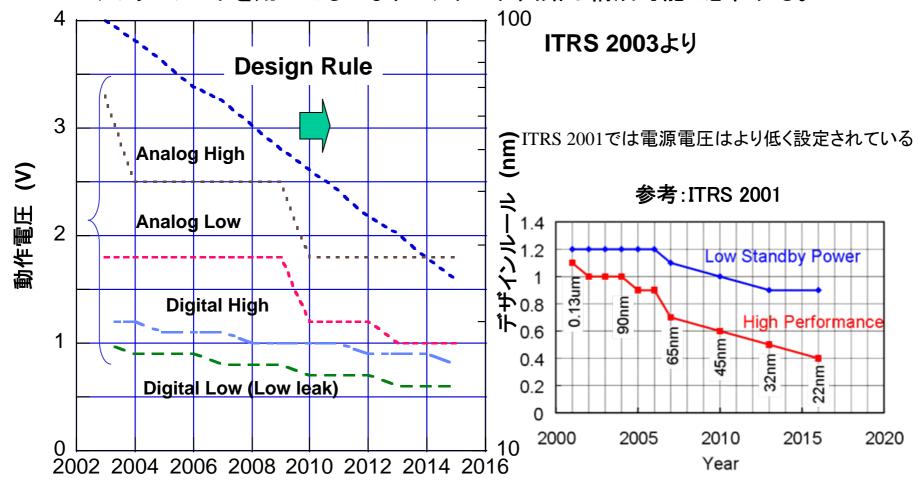

# 今後のSoCの動作電圧

今後は内部コアTrでも1V前後の動作電圧で推移。急激には低下しない。 コアトランジスタを用いてもかなりのアナログ回路は構成可能と思われる。

# ロードマップの限界

#### デザインルールが65nm辺りからfT\*Vはシリコンの限界を超える

#### kT/Cノイズ

トランジスタや抵抗は熱雑音を発生する。雑音電力は周波数帯域に比例するので、最終的には使用している容量により雑音電力が決まる。

- →高精度化=高ダイナミックレンジ化のためには容量か信号振幅を大きくしなければならない

- →電源電圧が下がってくると同一のダイナミックレンジを取るためには容量を大きくしなければならない

微細化で電源電圧が下がると高性能ADCが設計しにくくなる

kT/Cノイズは

$$V_n^2 = \frac{nkT}{C}$$

ここでnは関係する容量数

フルスケール入力電圧をV<sub>FS</sub>とおくと

$$SNR_{(dB)} = 10\log\left(\frac{CV_{FS}^2}{8nkT}\right)$$

2005.06.21

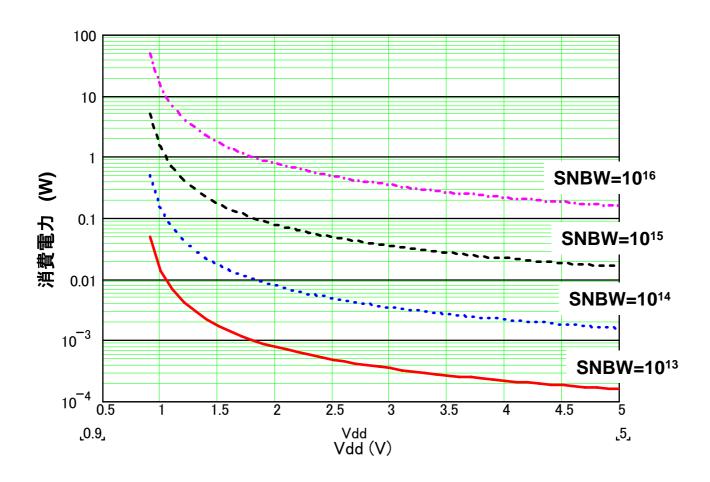

# 回路特性・電源電圧と消費電力

SNRで制約される場合の消費電力はSNRとGB積に比例し電源電圧に反比例する (ただし、回路の寄生容量効果は入れていない)

$$S_p = \frac{V_{pp}^2}{2}$$

$$S_p = \frac{V_{pp}^2}{2}$$

$GBW = \frac{g_m}{2\pi C} = \frac{I_{sink}}{2\pi CV_{eff}}$

$$N_p = 2\gamma \frac{kT}{C}$$

$$I_{sink} = \frac{8\gamma\pi kT \cdot V_{eff} \cdot SNR_{diff} \cdot GBW}{V_{pp}^{2}}$$

$$SNR_{diff} = \frac{CV_{pp}^2}{4\gamma kT}$$

$$P_{d} \approx \eta \cdot 8 \gamma \pi k T \cdot V_{eff} \cdot \frac{SNR_{diff} \cdot GBW}{V_{dd}}$$

$$C = \frac{4\gamma kT \cdot SNR_{diff}}{V_{pp}^2}$$

# 回路特性・電源電圧と消費電力

高SNR, 広帯域では電源電圧が下がると容量が増加し、消費電力が急増する

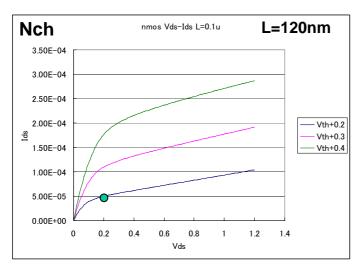

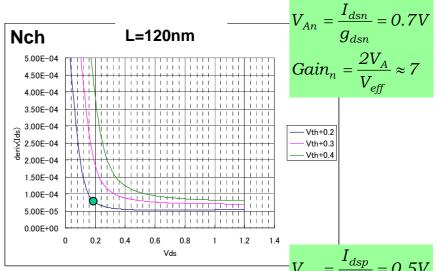

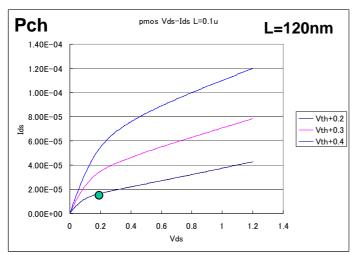

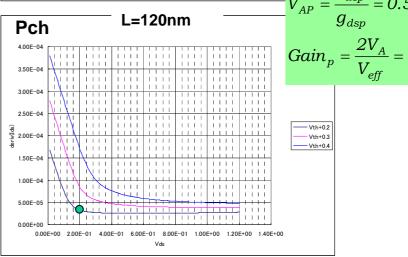

### 90nm CMOS の特性

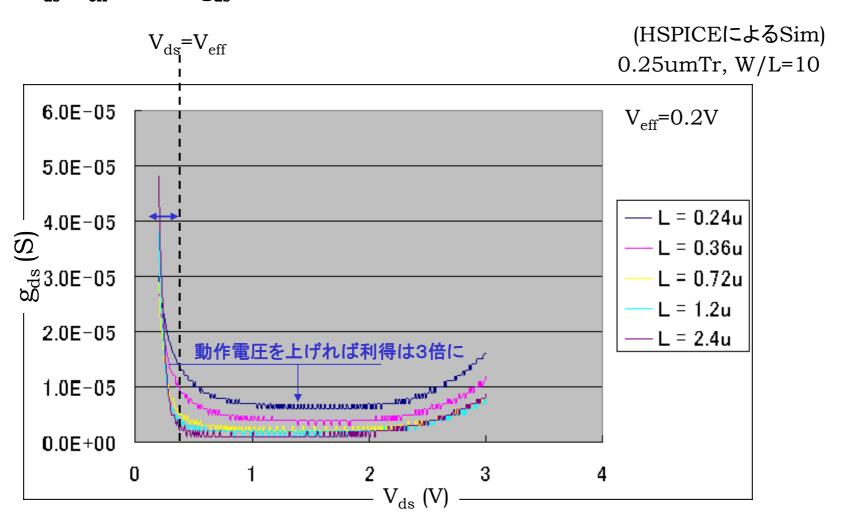

90nmデバイスはドレイン抵抗が極めて低いため10倍以下の利得しか取れない (0.25umでは数10倍の利得が取れる)

# g<sub>ds</sub>の特性

#### $V_{ds} > V_{eff}$ になっても $g_{ds}$ は大きく変化する。低電圧ではドレイン抵抗を上げられない。

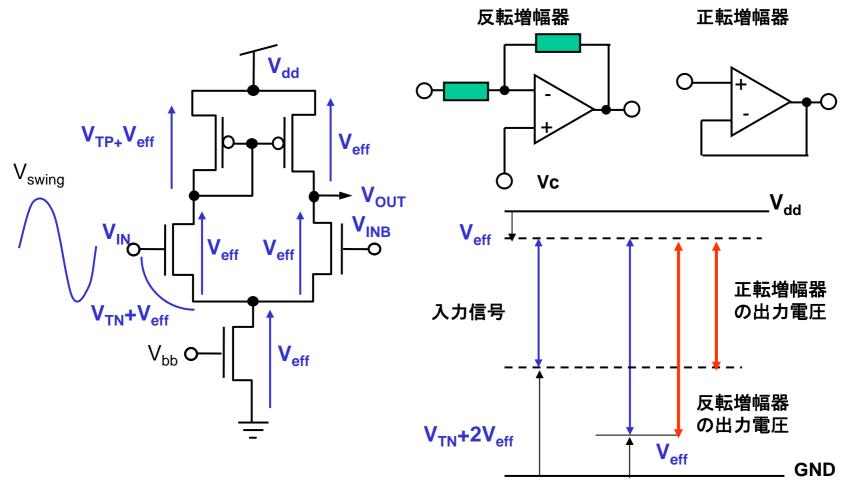

# アナログ回路の動作電圧

アナログ回路の動作電圧は回路形式、使用形態、しきい値電圧、有効ゲート電圧、信号振幅などで決まる

# 動作電圧を下げるには

- 反転増幅器の採用

- しきい値電圧が利かないような回路形式

- 動作電圧に関するVestの数を削減

- 入出力コモンモード電圧を合わせる

- 入出力コモンモード電圧差の調整

- ・ 差動形式の採用→信号振幅が2倍になる

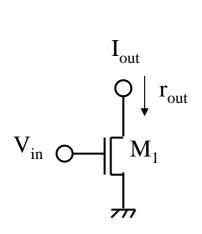

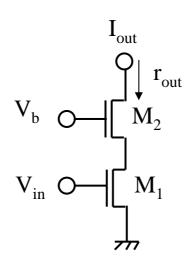

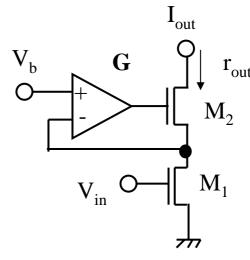

# 出力抵抗を上げる各種回路

カスコード回路だけでなく、OPアンプを用いたスーパーカスコードを用いると出力抵抗を 極めて高くできるためDC利得が上がる。

$$r_{out} \approx r_{ds}$$

(a) Source grounded ckt.

$$r_{out} \approx r_{ds1} (g_{m2} \cdot r_{ds2})$$

$\approx r_{ds1} \cdot G_o$

(b) Cascode ckt.

$$r_{out} \approx r_{ds1}(g_{m2} \cdot r_{ds2})$$

$r_{out} \approx r_{ds1}(g_{m2} \cdot r_{ds2}) \cdot G$

$\approx r_{ds1} \cdot G_o$   $\approx r_{ds1} \cdot G_o \cdot G$

(c) Super-cascode ckt.

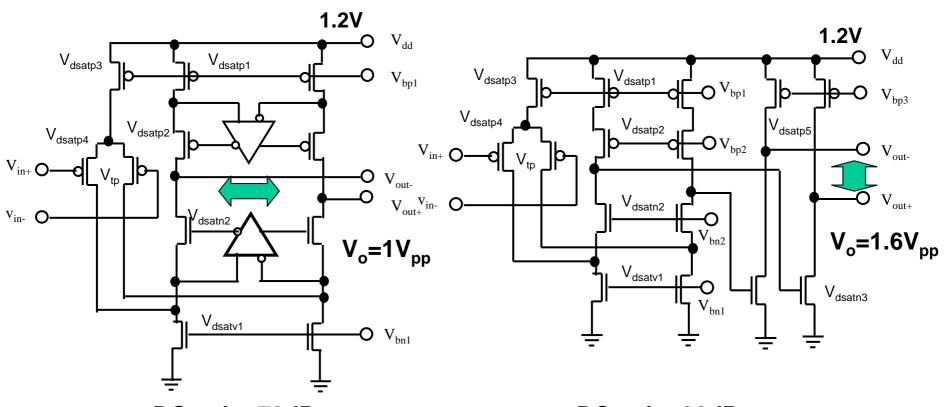

# 超低電圧OPアンプの設計方針

#### • 低分解能 · 超高速動作

- 低分解能のため振幅が低くても容量は小さくできる

- 超高速動作のために1段のカスコード回路を用いる

- 利得の低下にはスーパーカスコードを用いて対処する

- 入出力信号範囲の整合のためフォールディドカスコードを用いる

#### • 中分解能•高速動作

- 中分解能のため振幅を大きくとりできるだけ容量を小さくできる

- 振幅を大きく取り利得を大きくするために2段増幅にする

- 利得の低下にはスーパーカスコードを用いて対処する

- A出力信号範囲の整合のためフォールディドカスコードを用いる

- 2段増幅ではGBWをあまり上げれないので変換周波数が満足するか確認する

# 超低電圧アナログ回路

低電圧アナログ回路もできないことはないが回路が複雑になる。

DC gain=70dB GBW=10GHz 90nmCMOS DC gain=90dB GBW=5GHz 90nmCMOS

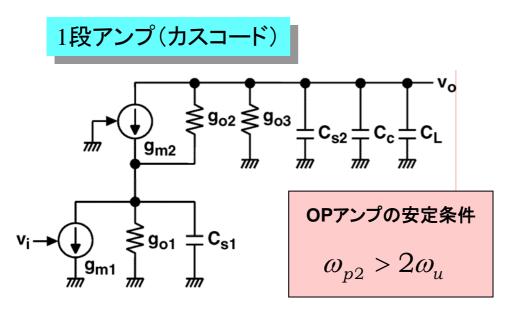

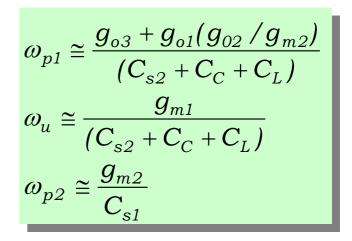

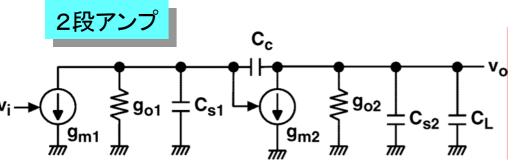

### CMOS基本アンプの極と安定性

OPアンプの帯域は安定性を考慮すると第2ポールで決まる。 第2ポールは実効的なfrにより決定される。

$$\omega_{p1} \cong \frac{g_{o1}(g_{02}/g_{m2})}{C_C}$$

$$\omega_u \cong \frac{g_{m1}}{C_C}$$

$$\omega_{p2} \cong \frac{g_{m2}}{C_{s1} + C_{s2} + C_L + (C_{s2} + C_L)\frac{C_{s1}}{C_c}}$$

2005.06.21 A. Matsuzawa,Titech

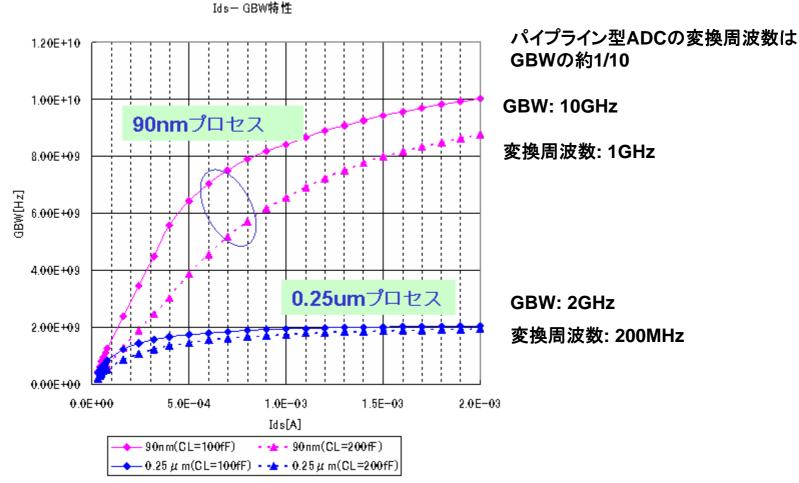

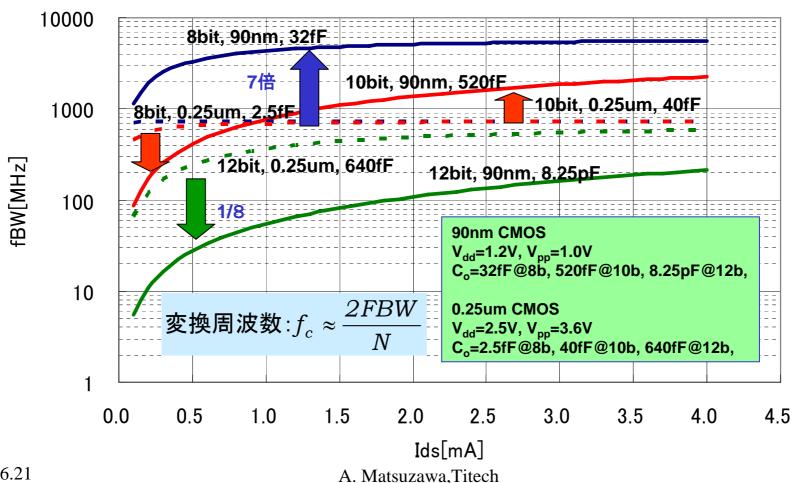

#### 90nm技術の効果

低電圧動作問題を解決すれば90nmを用いて、 8bitで1GHz, 10bitで500MHz程度のADCが実現可能かもしれない。 0.25um技術では200MHzの変換速度が限界である。

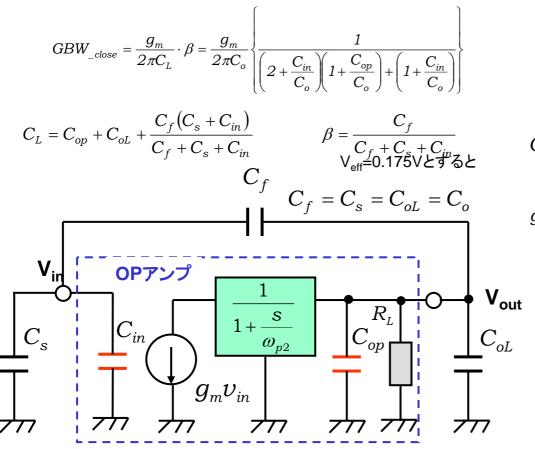

#### 動作電流と変換速度に対するデザインルール依存の推定

デザインルールにより取りうる信号振幅が変わるので、必要なSNRを確保するための帰還容量が変わる。また、ある動作電流における寄生容量が変わるので、この効果を入れて回路の応答を推定する。

N:分解能

#### 帰還容量の電圧振幅依存性を組み込む

$$C_o(fF) = 1.23 \times 10^{-4} \left(\frac{2^N}{V_{dd} - 4V_{eff}}\right)^2$$

$g_m = \frac{2I_{ds}}{V_{eff}} \Rightarrow g_m(mS) = 11.4 \times I_{ds}(mA)$

90nm:

$$C_{in}(fF) = 52 \times I_{ds}(mA),$$

$C_{op}(fF) = 95 \times I_{ds}(mA)$

0.25um :

$$C_{in}(fF) = 470 \times I_{ds}(mA)$$

,

$C_{op}(fF) = 780 \times I_{ds}(mA)$

パイプラインADCの増幅器の等価回路

### パイプラインADCの性能とデザインルール

低分解能は高速化が可能な微細デバイスが有利、高分解能は電源電圧が高く取れるデバイスが有利

2005.06.21

### パイプラインADCの性能とデザインルール

$SNR \propto C_{sig}V_{sig}^2$

緩いルール:信号容量が小さい(信号振幅が大きい)

微細ルール:信号容量が大きい(信号振幅が小さい)

変換速度

$$\propto GBW \propto \frac{g_m}{C_{tot}} = \frac{I}{C_{tot}} = \frac{I}{C_p I + C_{sig}}$$

C<sub>p</sub>:単位動作電流あたりの寄生容量

61

緩いルール:単位寄生容量が大きい

微細ルール:単位寄生容量が小さい

SNRが低く、信号容量がトランジスタの寄生容量よりも小さいときは微細トランジスタが高速化に有利。

SNRが高い場合は信号振幅が取れない微細トランジスタの信号容量が大きくなり、必要なGBWを確保するために大きな電流を流すことが必要となる。

このとき寄生容量も比例して増加するので微細トランジスタは高速化にも不利。

### アナログ回路のデザインルールと信号帯域

SNRを考慮しない場合、比較器の帯域はデザインルールの2乗に反比例する。 微細化は有効である。

$$GBW = \frac{g_m}{2\pi \left(WC_j + \frac{2}{3}C_{ox}LW\right)} = \frac{I_{sink}}{2\pi \left(WC_j + \frac{2}{3}C_{ox}LW\right)}V_{eff}$$

$$GBW = \frac{\mu V_{eff}}{2\pi L^2 \left(\frac{2}{3} + \frac{C_j}{k}\right)}$$

$$GBW = \frac{\mu V_{eff}}{2\pi L^2 \left(\frac{2}{3} + \frac{C_j}{k}\right)}$$

$$I_{sink} = \frac{\mu C_{ox}}{2} \frac{W}{L} V_{eff}^2$$

$C_{ox} = \frac{\kappa}{L}$

Feature size ( $\mu m$ )

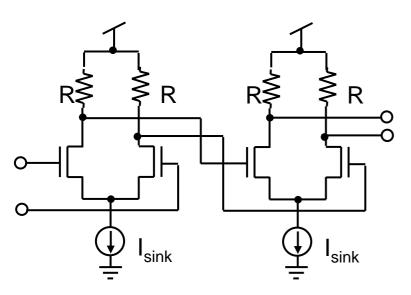

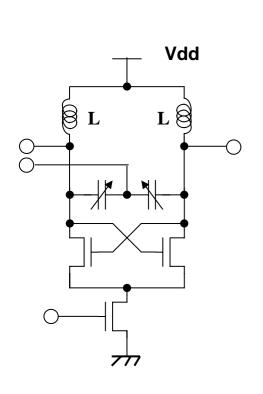

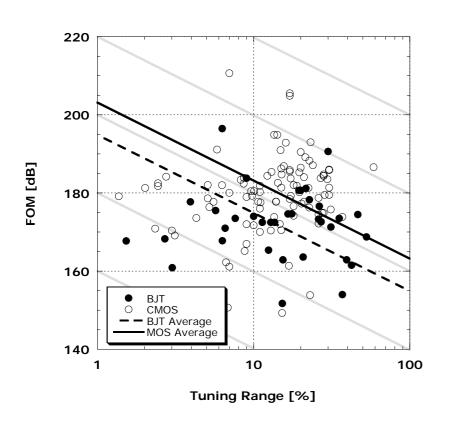

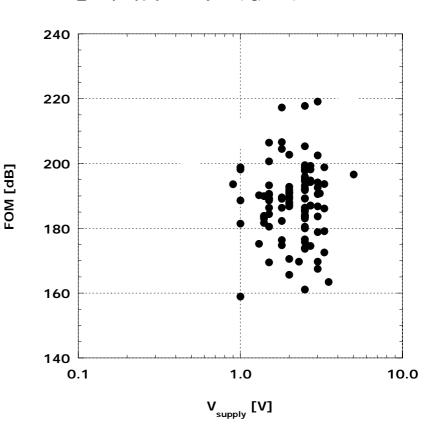

# 発振器

#### FoMは維持可能だが、低電圧化により位相ノイズは劣化する

$$L(f_{m}) = \frac{1}{2} \cdot \frac{1}{Q^{2}} \cdot \left(\frac{f_{o}}{f_{m}}\right)^{2} \cdot \frac{FkT}{P_{RF}} = \frac{1}{2} \cdot \frac{1}{Q^{2}} \cdot \left(\frac{f_{o}}{f_{m}}\right)^{2} \cdot \frac{FkT}{\left(\frac{V_{o}^{2}}{2r_{o}}\right)}$$

$$L_{min}(f_{m}) = kT \frac{\gamma}{V_{dd}} \frac{\omega_{o}L}{2Q} \left(\frac{1}{V_{dd}} + \frac{2}{V_{eff}}\right) \left(\frac{f_{o}}{f_{m}}\right)^{2}$$

$$FoM = \left(\frac{f_{o}}{f_{m}}\right)^{2} \frac{1}{L(f_{m})V_{dd}I}$$

$$FoM \approx \frac{Q^{2}}{\gamma\pi \cdot kT \cdot F} \quad or \quad \frac{4Q^{2}}{\gamma\pi \cdot kT \cdot \left(1 + \frac{V_{dd}}{V_{off}}\right)}$$

### CMOS VCOOFoM

#### MOSがバイポーラよりも良い特性を示す

# 低電圧化で若干悪くなっているが電圧依存性はあまり強くない

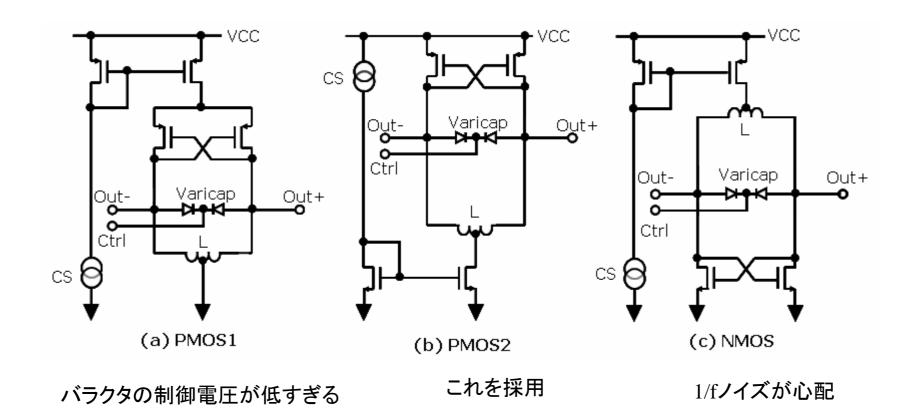

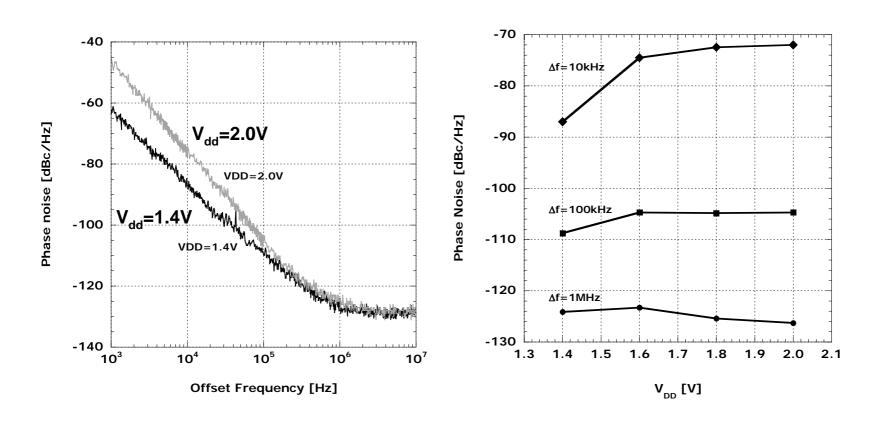

# 低電圧VCO

# 低電圧VCOの特性

小信号解析では電源電圧が高いほうがノイズ特性が良くなるはずであるが、大振幅では 回路の非線形性が高くなるので周波数変換作用によりノイズが増大することもある。 この回路は熱雑音は2Vの方が小さいが、低周波雑音は1.4Vの方が小さくなっている。

#### **MOS LNA**

MOS LNAのノイズはゲート抵抗をゲート分割などで十分に低減し、十分なgmを与えたら frが向上するほど少なくなる。したがって微細化に伴い、ノイズは減少している。

$$F \approx 1 + \frac{r_g}{r_s} + \frac{2}{3g_m r_s} + \left(\frac{\omega_0}{\omega_T}\right)^2 \frac{2g_m r_s}{3}$$

$$\begin{array}{c} 8.0 \\ 7.0 \\ 6.0 \\ 4.0 \\ 1.0 \\ 0.0 \end{array}$$

$$\begin{array}{c} 8.0 \\ 4.0 \\ 1.0 \\ 0.0 \end{array}$$

$$\begin{array}{c} 8.0 \\ 4.0 \\ 1.0 \\ 0.0 \end{array}$$

$$\begin{array}{c} 8.0 \\ 4.0 \\ 1.0 \\ 0.0 \end{array}$$

$$\begin{array}{c} 6.0 \\ 0.0 \\ 1.0 \\ 0.0 \end{array}$$

$$\begin{array}{c} 6.0 \\ 0.0 \\ 1.0 \\ 0.0 \end{array}$$

$$\begin{array}{c} 6.0 \\ 0.1 \\ 0.1 \\ 0.1 \\ 0.0 \end{array}$$

$$\begin{array}{c} 6.0 \\ 0.1 \\ 0.1 \\ 0.0 \end{array}$$

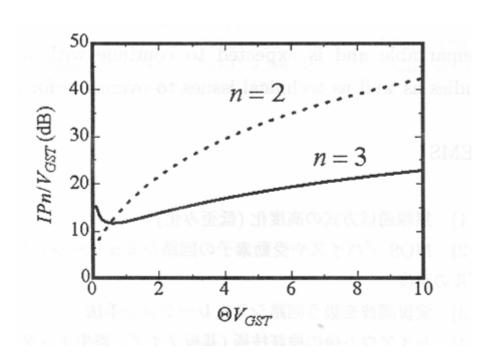

# 速度飽和効果と歪

- ・V<sub>eff</sub>が大きいほど歪が小さい

- ・微細化により歪は小さくなる(速度飽和効果)

$$I_{ds} = K \frac{W}{L} V_{eff}^2 \frac{1}{1 - \lambda V_{ds}} \frac{1}{1 + \Theta V_{eff}}$$

$$\Theta = \theta + \frac{\mu_0}{2v_{sat}L}$$

$$IIP_2 = V_{eff} (2 + \Theta V_{eff}) (1 + \Theta V_{eff})$$

$$IIP_3 = \sqrt{\frac{4V_{eff}}{3\Theta} \left(2 + \Theta V_{eff}\right) \left(1 + \Theta V_{eff}\right)^2}$$

#### 低電圧アナログスイッチ特性

- ・低電圧ではオン抵抗が大きな入力電圧依存を持つ(4倍)

- ·SOIはオン抵抗の入力電圧依存性が小さい(2倍)

低いVァと小さなバックゲート効果

同一リーク電流になるようにV<sub>T</sub>を調整

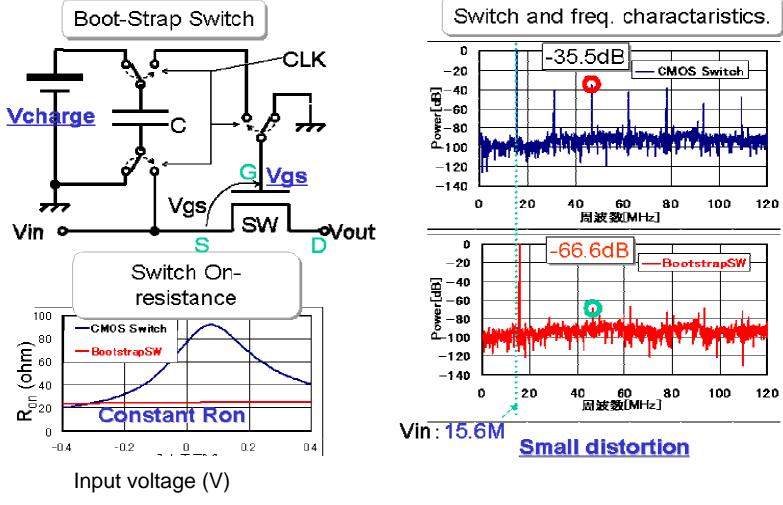

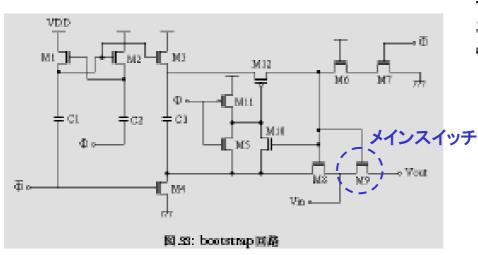

# ブートストラップ回路

オン抵抗の入力電圧依存性は歪を発生させる。これを抑制するために ゲート・ソース間に一定電圧を与えるブートストラップ回路が用いられている。

# ブートストラップ回路

ソース・ゲート間に一定電圧をかけてオン抵抗を減らすとともに、 電圧依存性を小さくする回路が可能である。 ただし、バックゲート効果により完全には補償できない。 また、容量により面積が大きくなる。

図 37: bootstrapSW のオン抵抗の入力依存性

### **ΣΔ型ADC**

ADC高分解能化へのシステム的アプローチ

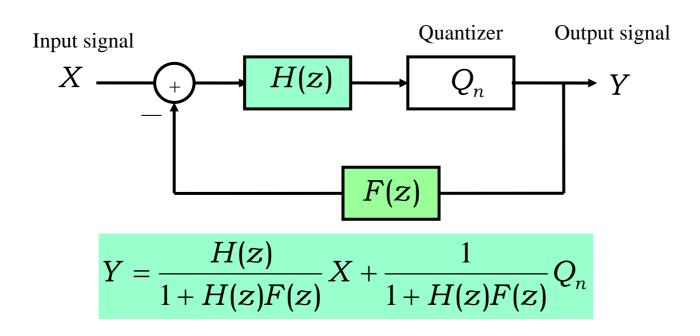

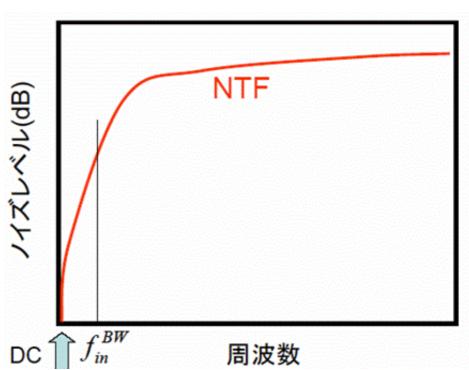

### ΣΔ変調器の汎用的システム表現

$$\frac{H(z)}{1+H(z)F(z)}$$

$$\frac{1}{1+H(z)F(z)}$$

**STF: Signal Transfer Function**

信号帯域に対してフラットな特性

**NTF:** Noise Transfer Function

ノイズに対してシェーピングする

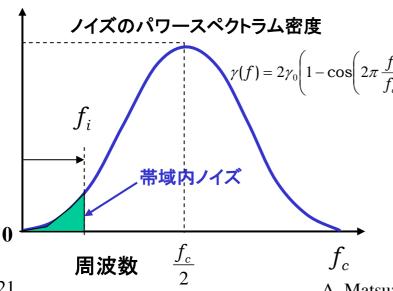

### ノイズ電力

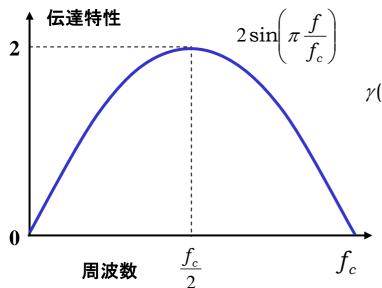

### ノイズのパワースペクトラム密度を求める

$$\gamma(f) = \gamma_0 H(f)^2 = 4\gamma_0 \sin\left(\pi \frac{f}{f_c}\right)^2 = 2\gamma_0 \left(1 - \cos\left(2\pi \frac{f}{f_c}\right)\right)$$

ノイズはf<sub>e</sub>/2まで分布しているので

$$\gamma_0 \frac{f_c}{2} = \frac{\Delta^2}{12} :: \gamma_0 = \frac{\Delta^2}{6f_c}$$

### 帯域fiまでのノイズ電力は、

クトラム密度

$$N_{q_-eff} = \gamma_0 \int_0^{f_i} \gamma(f) df = \frac{2\Delta^2}{6f_c} \int_0^{f_i} \left(1 - \cos\left(2\pi \frac{f}{f_c}\right)\right) df$$

$$\gamma(f) = 2\gamma_0 \left(1 - \cos\left(2\pi \frac{f}{f_c}\right)\right) = \frac{\Delta^2}{3f_c} \left[f - \frac{f_c}{2\pi} \sin\left(2\pi \frac{f}{f_c}\right)\right]_0^{f_i} = \frac{\Delta^2}{3f_c} \left(f_i - \frac{f_c}{2\pi} \sin\left(2\pi \frac{f_i}{f_c}\right)\right)$$

$$= \sin\left(2\pi \frac{f_i}{f_c}\right) \approx 2\pi \frac{f_i}{f_c} - \frac{1}{3!} \left(2\pi \frac{f_i}{f_c}\right)^3$$

で近似すると、

$$= \frac{\Delta^2}{3f_c} \cdot \frac{f_c}{2\pi} \frac{1}{6} \cdot \pi^3 \cdot \frac{1}{M^3} = \frac{\pi^2}{36} \Delta^2 \frac{1}{M^3}$$

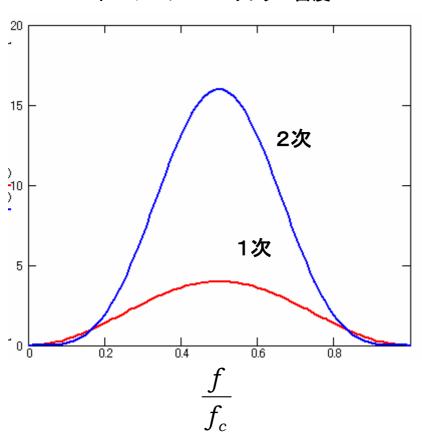

## 高次の効果

#### ノイズのパワースペクトラム密度

#### 1次ΣΔ変調

$$\gamma(f) = \gamma_0 H(f)^2 = 4\gamma_0 \sin\left(\pi \frac{f}{f_c}\right)^2 = 2\gamma_0 \left(1 - \cos\left(2\pi \frac{f}{f_c}\right)\right)$$

$$N_{q(1st\, order)} = \frac{\Delta^2 \pi^2}{36} \left(\frac{1}{M}\right)^3$$

#### 2次ΣΔ変調

$$\gamma(f) = \gamma_0 H(f)^2 = 16\gamma_0 \sin\left(\pi \frac{f}{f_c}\right)^4$$

$$N_{q(2nd \, order)} = \frac{\Delta^2 \pi^4}{60} \left(\frac{1}{M}\right)^5$$

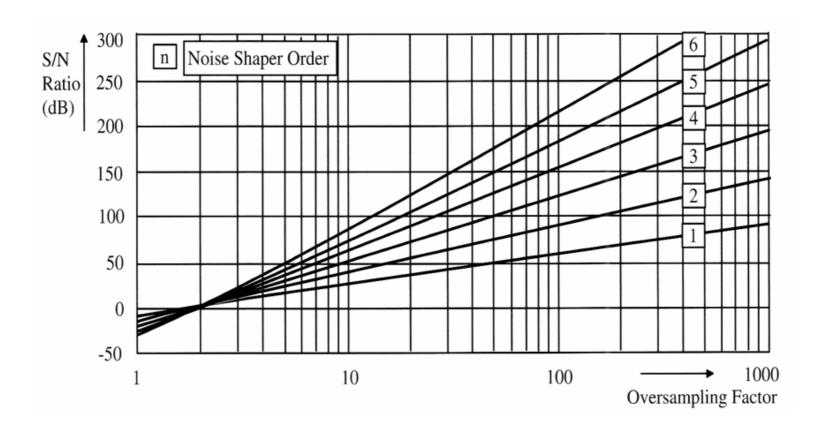

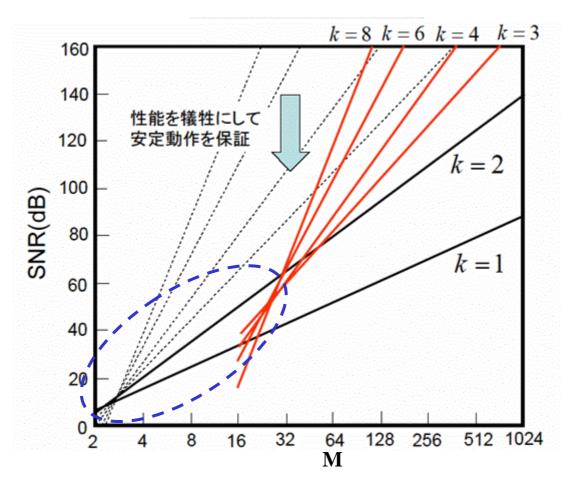

# SNR:次数とオーバーサンプリング比

システムの次数を上げればSNRは上がるが、システムが不安定になるので、このような高いSNRは実際は困難である。

1ビット量子化の場合 理論上の限界値

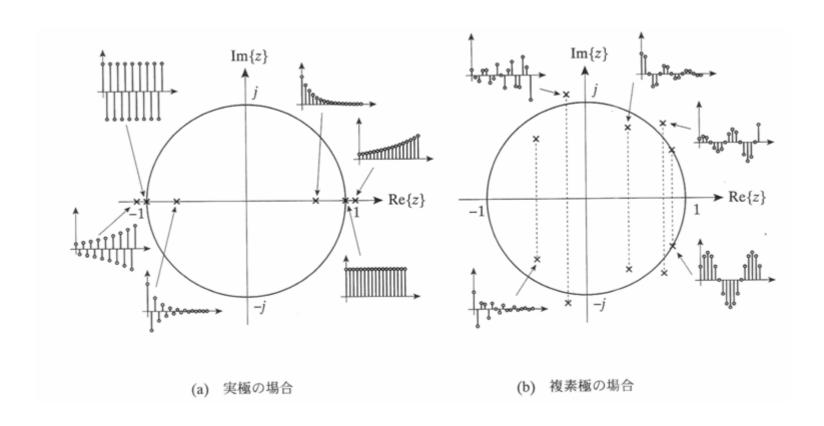

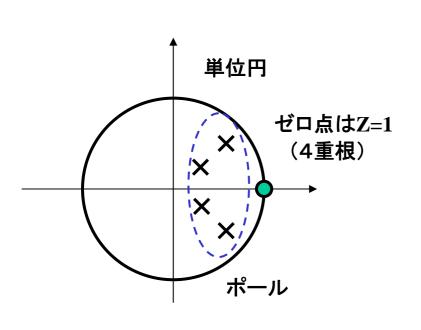

## 極の位置とシステムの安定

#### ポールが単位円の内側にあれば安定

高次のシステムでは安定性が取りにくい

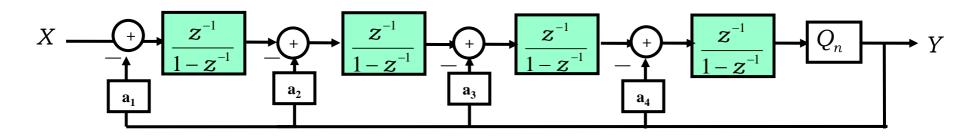

## 4次ΣΔ変調器

$$NTF: \frac{\left(1-z^{-1}\right)^4}{\left(1-z^{-1}\right)^4+a_4\left(1-z^{-1}\right)^3z^{-1}+a_3\left(1-z^{-1}\right)^2z^{-2}+a_2\left(1-z^{-1}\right)^1z^{-3}+a_1z^{-4}}$$

高次の場合は不安定になるので、係数を調整して安定になるように根の位置を調整する。

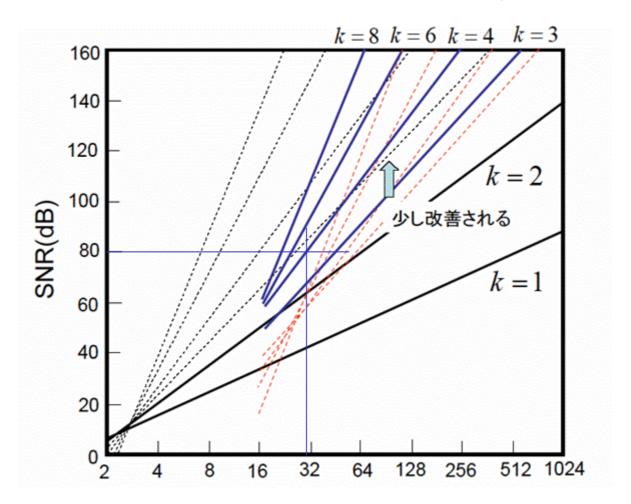

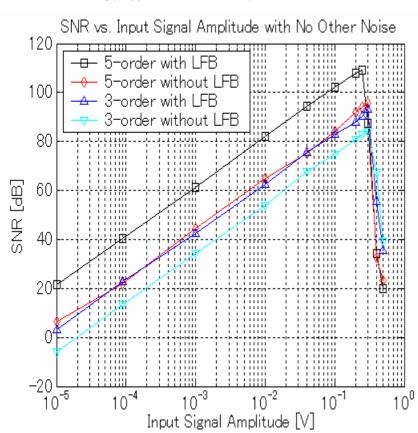

### 安定条件でのSNR

系を安定にすると低オーバーサンプリング比においてSNRが著しく劣化するこれでは低いオーバサンプリング比では2次程度にした方が高いSNRが得られる。

阪大 谷口教授より

# ポールとゼロおよび周波数特性

#### 系が安定なためにはポールが単位円の内側になければならない

阪大 谷口教授より

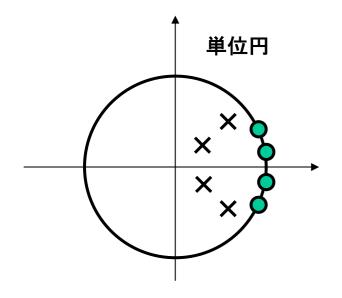

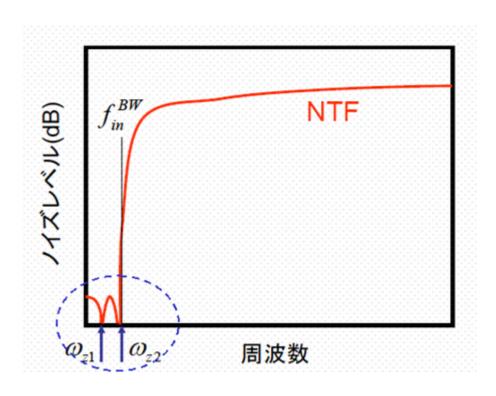

## ゼロ点の分散

### ゼロ点を分散させて信号通過帯域内において深い減衰特性を作る

ポールは安定性確保にため余りいじれない

ゼロ点を |z|=1 上で分散させる

#### 信号通過域において深い減衰特性が得られる

阪大 谷口教授より

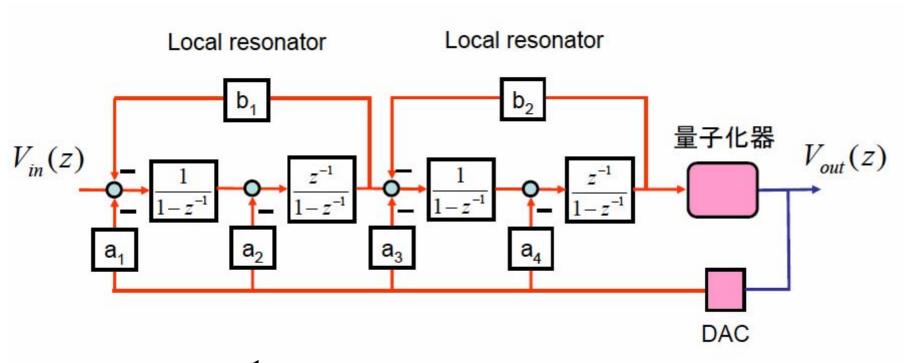

## ローカル共振回路

ゼロ点を分散させるために積分器に帰還をかける。

$$NTF: rac{1}{1+H(z)F(z)}$$

$H(z)$ の極はNTFのゼロになる

# ゼロ点分散の効果

#### SNR=80dBにはM=32以上が必要

阪大 谷口教授より

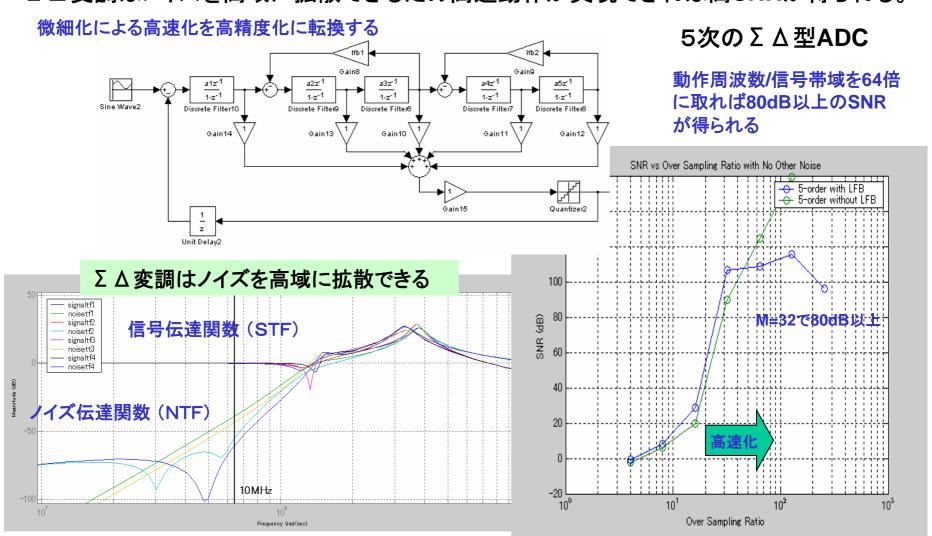

### **Σ** Δ型ADC

### ΣΔ変調はノイズを高域に拡散できるため高速動作が実現できれば高SNRが得られる。

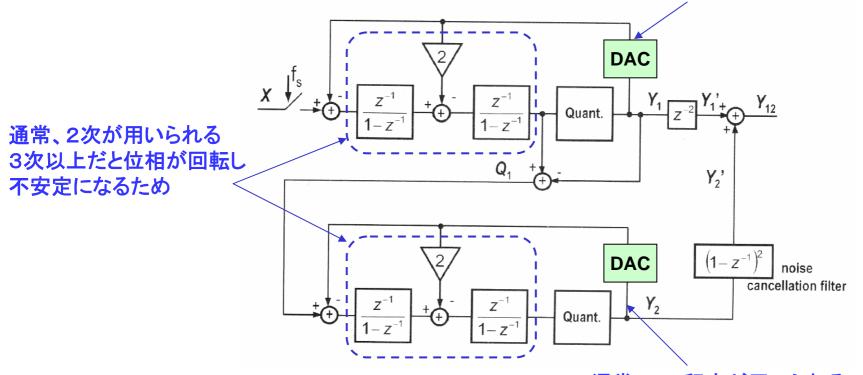

### 2-2 cascaded ΣΔ型ADC

2-2 cascaded Σ Δ型ADCも良く用いられる。

2次のフィードバックなので安定で、オーバーサンプリング率が低いところでは高いSNRが得られる。ただし、初段の誤差に対してはノイズシェーピング効果が薄いため 通常、1bitが用いられる80dB以上のダイナミックレンジは確保しにくい。 タビットだと誤差を生じるため

通常、3bit程度が用いられる 誤差を生じても影響が少ないため

# 開発例

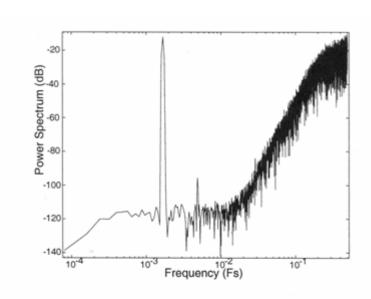

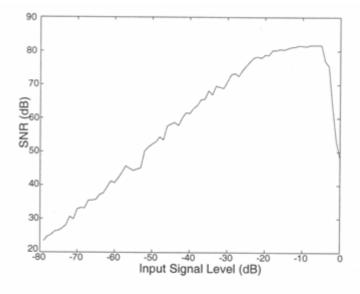

# 0.35um CMOS, Pd=16.8mW, 3V supply SNR=81dB, SNDR=80dB for DCS1800 (GSM)

Figure 6.18. DCS1800 Mode Output Spectrum:  $f_{in}=25KHz,\,f_s=12.8MHz,\,{\rm Input}$  Amplitude 1Vpp

Figure 6.19. DCS1800 Mode SNR versus. Input Amplitude:  $f_{in} = 25KHz$ ,  $f_s = 12.8MHz$

X. Li and M. Ismail, "Multi-Standard CMOS Wireless Receivers" Kuluwer

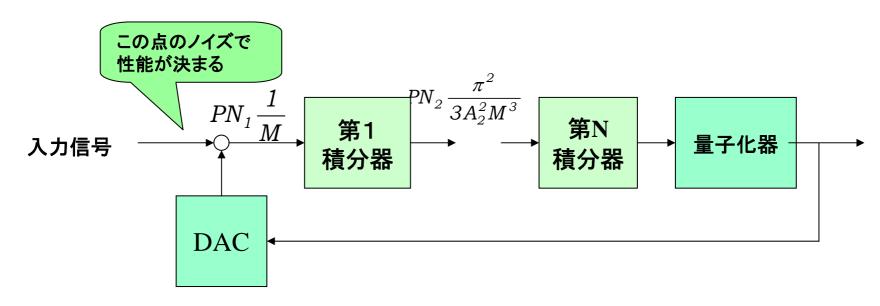

### 必要な容量値

KT/Cノイズは殆ど初段で決まり、オーバーサンプル比だけ減少する。 GSMのようにDR=80dBも必要とする場合はオーバーサンプリング比率が高くとも かなりの大きさの容量を必要とする。

各段のノイズ電力とその寄与

$$P_{N,tot} = PN_1 \frac{1}{M} + PN_2 \frac{\pi^2}{3A_2^2 M^3} + PN_3 \frac{\pi^4}{5A_3^2 M^5} + PN_4 \frac{\pi^6}{7A_4^2 M^7}$$

A: 入力端からそのステージまでの利得

Noise Budget and Capacitor Scaling of Integrators

| Noise Budget<br>Capacitor<br>Sizing | Integrator<br>I | Integrator<br>II | Integrator<br>III | Integrator<br>IV |

|-------------------------------------|-----------------|------------------|-------------------|------------------|

| GSM (15bits,<br>95dB)               | 50uVrms         | 177uVrms         | 1mVrms            | 3mVrms           |

| Capacitor Sizes                     | 3.2pF           | 0.5pF            | 0.024pF           | 0.002pF          |

| DECT (12bits,<br>75dB)              | 100uVrms        | 177uVrms         | 400uVrms          | 1mVrms           |

| Capacitor Sizes                     | 0.8pF           | 0.5pF            | 0.15pF            | 0.016pF          |

| WCDMA<br>(7bits, 48dB)              | 560uVrms        | 560uVrms         | 560uVrms          | 560uVrms         |

| Capacitor Sizes                     | 0.025pF         | 0.05pF           | 0.076pF           | 0.05pF           |

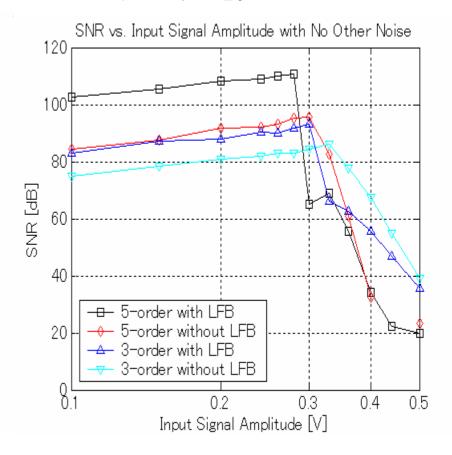

## 低電圧動作課題:入力振幅-SNR特性

- オペアンプの許容振幅0.5Vに対し, 0.25~0.3Vの入力振幅で飽和

- 入力振幅とSNRの特性

#### ■ SNR劣化部分を拡大

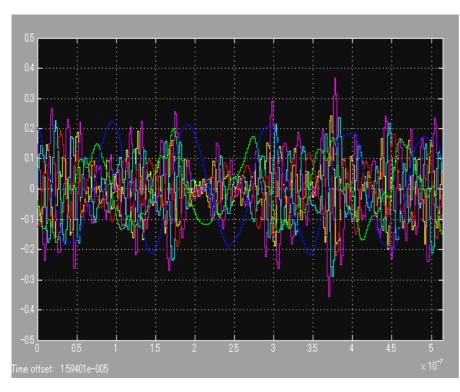

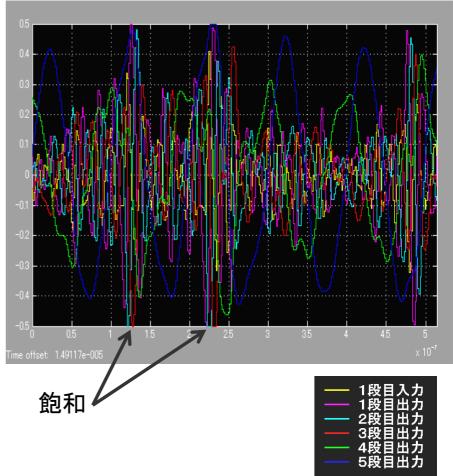

# 各積分器出力の時間波形

■ 入力振幅: 0.2V

(5次LFB付きのフィルタを使用)

■ 入力振幅: 0.35V

### Σ Δ ADCの課題

ΣΔ型ADCの性能は最終的に初段のSNRで決まり、この部分のノイズはM分の1にしか下がらない。更に信号飽和により入力振幅を上げられないのでMは最低8以上なければ優位性が無い。80dB程度のSNRを得るには16から32倍のMが必要であろう。

入力端のノイズはオーバーサンプリング比でしか減少しない。 積分器の飽和レベルは帰還信号振幅の半分程度である。

パイプライン型ADC:  $CV_{sig}^2$

同一OPアンプ同一容量で構成すると

$\Sigma$  デルタ型ADC:  $CV_{sig}^2 \cdot M$

Mは8以上なければパイプライン型ADCの SNRを超えられない

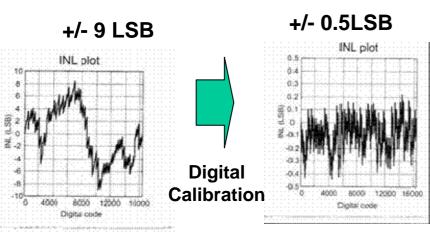

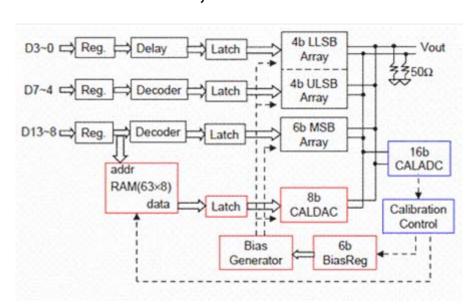

## ばらつきの抑制:デジタル補正技術

微細化技術を用いると周波数特性が向上し、低消費電力になるが、ばらつきが増大する。 そこでデジタル補正技術でこれに対処することが盛んになっている。 微細化によりデジタル部のオーバーヘッドが小さくなっている。

Y. Cong and R. L. Geiger, Iowa state university, ISSCC 2003

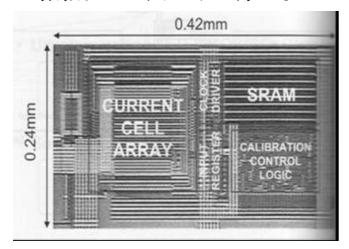

面積: 1/50

14b 100MS/s DAC

消費電力: 1/20 1.5V, 17mW, 0.1mm², 0.13um

SFDR=82dB at 0.9MHz, 62dB at 42.5MHz

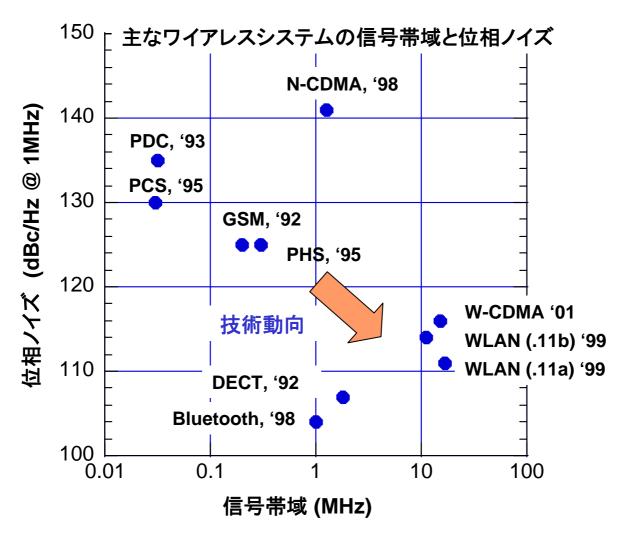

### ワイアレスシステム仕様の動向

#### ワイアレスシステムは広帯域・低ダイナミックレンジの方向へ

## 今後の方向性

### デバイス動向

- ·微細化

- •高速•高周波•広帯域化

- ·低電圧化

- ・ばらつき・ノイズの増大

- 面積コストアップ

### 回路動向

- ·高速·高周波·広帯域化

- · 高利得困難

- 高ダイナミックレンジ困難

- •高精度化困難

### システム動向

- ·高速·高周波·広帯域化

- ・低ダイナミックレンジ化

- ・マルチバンド・マルチスタンダード化

- ·SoC化

- ・低コスト化・省面積化

- ·短開発TAT

- ・テスト容易化

- ・ノイズ耐性強化

### 今後の方向性

- ・微細化による高速・高周波・広帯域化を活かす

- ・本質的に必要なアナログのみを残す ・インダクタなどの受動部品の削減

- -デジタル技術の徹底活用

- ・デジタル制御・補正の活用 (ばらつきや不安定性の克服と最適化)

- ・ΣΔ変調技術による高精度化

## 第4世代携帯電話とアナログ回路

### 第4世代のワイアレスシステム

- 超高速データ伝送 100Mbps ~1Gbps

- 空間並列のMIMOの利用

- 変復調はOFDMを使用

- マルチスタンダードへの対応が必要

- 微細CMOS (60nm~45nm?)を使用

### • アナログ回路への要求

- ADCの高速化 10b, 400MHz程度 低電力化

- ADCの性能可変化 (GSMなどの高DRにはΣΔ型ADCで対応)

- 微細CMOSでのアナログ回路のオンチップ化

- 65nm以下のCMOSを用いた1V程度の低電圧アナログ回路が必要

### まとめ

#### · ワイアレスシステムの動向

- 超高速信号伝送

- マルチバンド・マルチスタンダード ソフトウエア無線技術ベース

- デジタル部の高速化・高集積化 65nm程度の微細CMOSが不可欠

- アナログへの要求

- RFのマルチバンド化 BBのマルチスタンダード化

- ADCの超高速化 高精度化も必要

- \_ 占有面積の低減 低電圧動作

- 微細化デバイス

- f<sub>T</sub>の向上(寄生容量の低下)

- 動作電圧低下 利得の低下

- ゲートリーク電流増加

- スイッチ特性の劣化

- 低電圧アナログ回路

- 信号振幅の減少に伴うノイズの増大 ダイナミックレンジの低下

- 高速化は可能だが 高増幅率回路は困難

- 高SNR→高容量·高利得→速度低下·電力増加

- 今後の方向性

- 高周波化・高速化・広帯域化の方向へ

- 高SNRはΣΔ変調技術を活用(ΣΔ変調:高速化→高SNRだが 限界も)

- 本質的に必要なアナログ回路だけを残し、デジタルへ